#### 1 Introduction

The MuSLIC, a chipset of three highly sophisticated ICs, bridges the gap between the analog and the digital signal transmission in modern telecommunication systems.

This highly integrated chip set supports to realize an extremely compact Analog Subscriber Line Interface Module. Only a few external components are required and there is no trimming or adjustment necessary to meet worldwide recommendations.

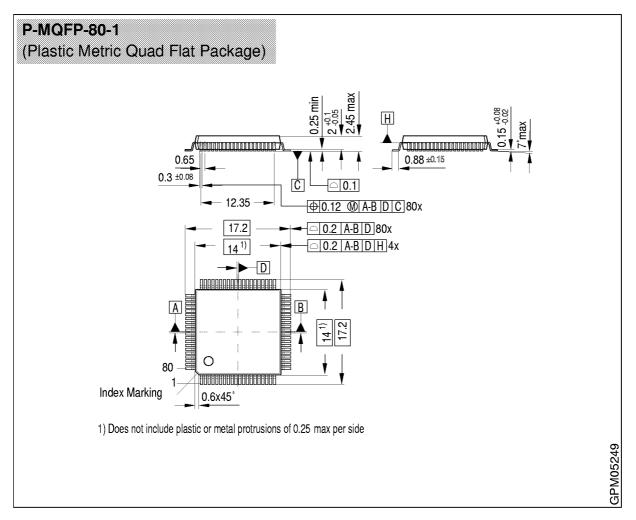

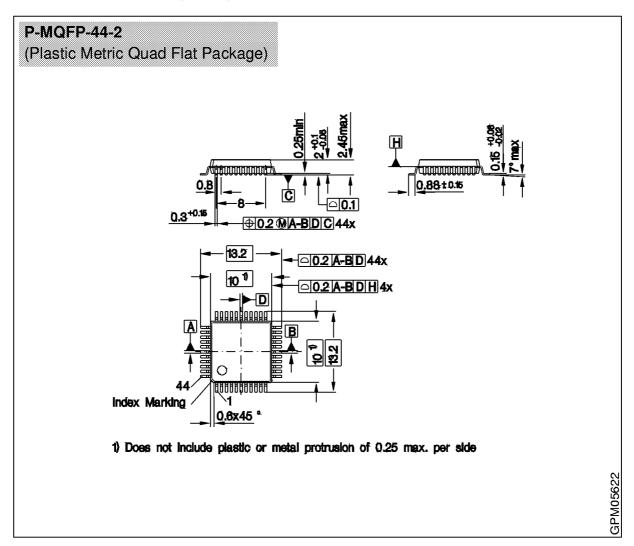

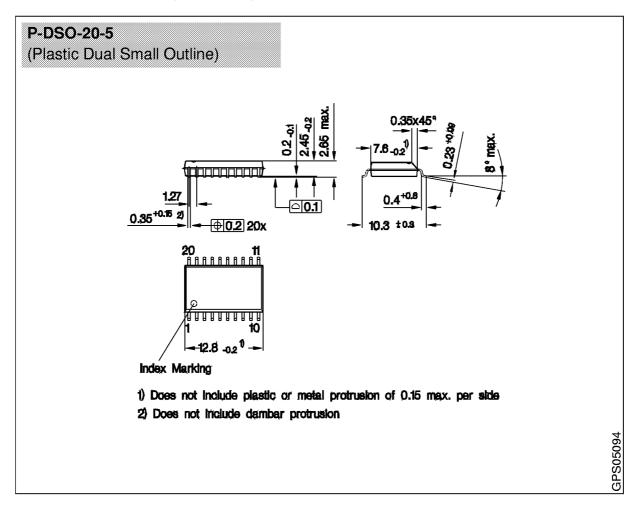

Each device is made of the best fitting technology (CMOS, BiCMOS and Smart Power Technology) and the standard SMD-packages P-MQFP and P-DSO are used.

The chipset consists of the following three ICs:

| • | PEB 31665 | (MuPP | Multichannel | Processor for POTS) | ) |

|---|-----------|-------|--------------|---------------------|---|

|---|-----------|-------|--------------|---------------------|---|

- PEB 3465 (QAP Quad Analog POTS)

- PEB 4165 (AHV-SLIC Advanced High Voltage Subscriber Line Circuit)

# Multichannel Subscriber Line Interface Concept MuSLIC

PEB 3465 PEB 31665 PEB 4165

Version 1.0 CMOS

#### 1.1 Features

- Chip set of three well fitted chips optimized for a 16 POTS-base system

- Including all low and high voltage SLIC functions

- · Only a few external components are required

- · No trimming or adjustments are required

- Specification according to relevant ITU-T, LSSGR and DTAG recommendations

- Digital signal processing technique

- Advanced low power CMOS and BiCMOS<sup>1)</sup> and Smart Power technology

- PCM encoded digital voice transmission (A-Law or μ-Law)

- Two serial IOM-2 (GCI) Interfaces with together 6 pins

- 12 Pin, 8 bits parallel microcontroller interface

- High performance AD and DA Conversion

- Programmable digital filters for

- Impedance matching

- Transhybrid balancing

- Frequency response

- Gain

- · Advanced test capabilities

- Integrated line and circuit tests

- Two programmable tone generators

7

<sup>1)</sup> Abbreviations see chapter 10.3

Type

Ordering Code

Package

PEB 3465 V1.0

on request

P-MQFP-80-1

PEB 31665 V1.0

on request

P-MQFP-44-2

PEB 4165 V1.0

on request

P-DSO-20

## **SIEMENS**

Introduction

04.97

- Fully digital programmable DC-Characteristic

- Programmable Constant Current from 0 to 50 mA

- Programmable Resistive Values from 0 to  $2 \times 500 \Omega$

- Programmable Constant Voltage

- Programmable Integrated Teletax Injection and Filtering during Active in Onhook and Offhook

- Programmable up to 10 Vrms at Ring/Tip-wire of the AHV-SLIC

- Programmable frequency (12/16 kHz)

- Polarity reversal (programmable soft or hard)

- Integrated (balanced) Ringing Generation with zero crossing injection

- Programmable frequency between 16.6 and 70 Hz

- Programmable amplitude up to 85 Vrms at Ring/Tip-wire of the AHV-SLIC

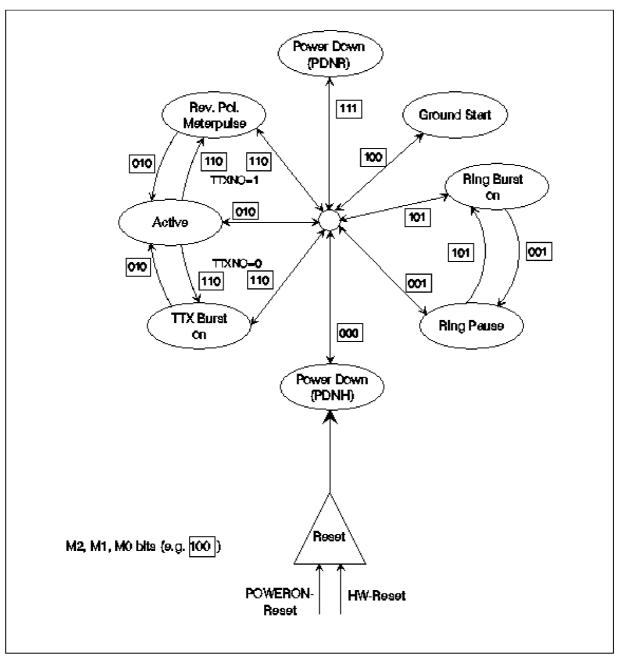

- Three operating modes: Power Down, Active and Ringing

- Offhook detection with programmable thresholds for all operating modes

- Integrated Ring Trip Detection with zero crossing turn off function

- Ground Start and Loop Start possible

- Integrated checksum calculation for CRAM (AC and DC separated)

- Linecard Identification

- Sensing of transversal and longitudinal line current

- Battery voltage 24 V ... 80 V; Auxiliary voltage + 5 V... + 85 V

- Boosted battery mode with up to 150 V supply for long telephone lines and up to 85 Vrms balanced ringing

- Reliable 170 V Smart Power Technology

- Standard SMD packages: P-MQFP-44 and P-MQFP-80 for the low voltage parts and small power package P-DSO-20 for the high voltage device

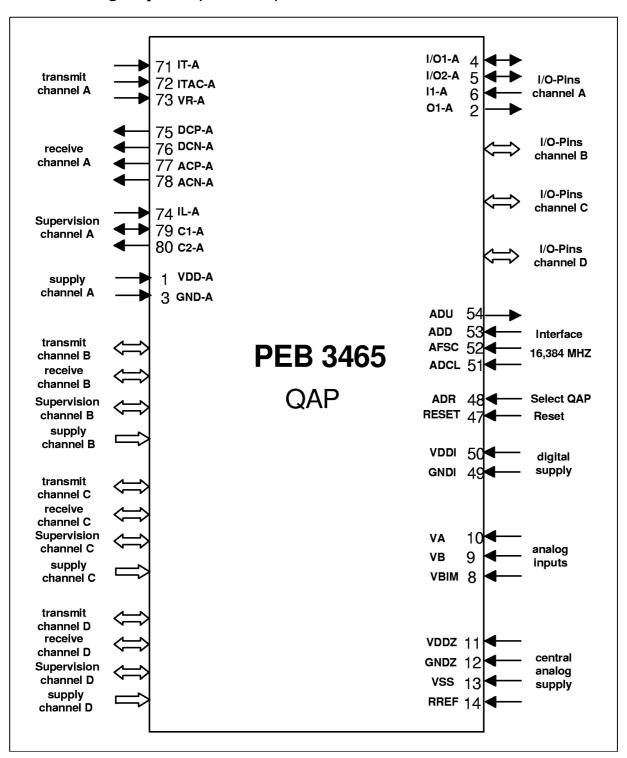

### 1.2 Logic Symbol (PEB 3465)

Figure 1

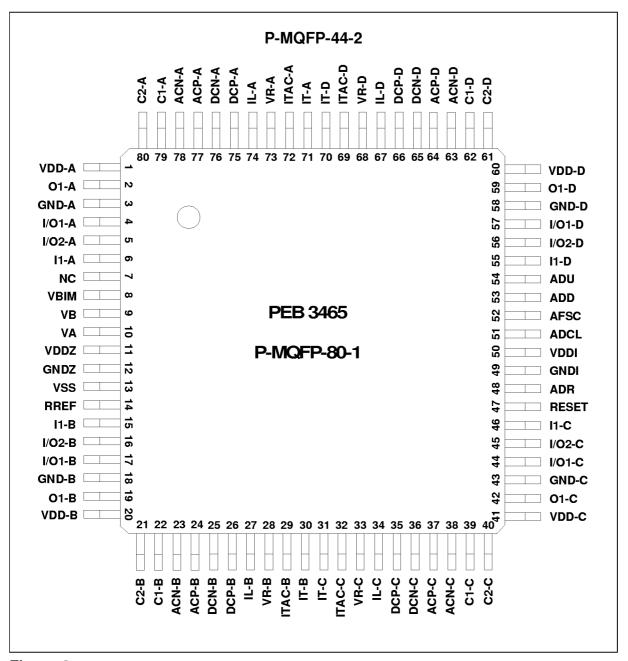

### 1.2.1 Pin Configuration (PEB 3465)

Figure 2

## 1.2.2 Pin Definition and Functions (PEB 3465)

The following tables group the pins according to their functions. They include pin number, pin name, type, a brief description of the function, and cross-references referring to the sections in which the pin functions are discussed.

Table 1 Pin Definition and Functions (PEB 3465)

| Pin No. | Name      | Туре | Function                                | Reference |

|---------|-----------|------|-----------------------------------------|-----------|

| Power S | upply Pin | ıs   |                                         |           |

| 1       | VDD-A     | _    | + 5 V Analog Supply Voltage (channel A) |           |

| 20      | VDD-B     | -    | + 5 V Analog Supply Voltage (channel B) |           |

| 41      | VDD-C     | _    | + 5 V Analog Supply Voltage (channel C) |           |

| 60      | VDD-D     | _    | + 5 V Analog Supply Voltage (channel D) |           |

| 3       | GND-A     | _    | Analog Ground (channel A)               |           |

| 18      | GND-B     | _    | Analog Ground (channel B)               |           |

| 43      | GND-C     | _    | Analog Ground (channel C)               |           |

| 58      | GND-D     | _    | Analog Ground (channel D)               |           |

| 11      | VDDZ      | _    | + 5 V Analog Supply Voltage (bias)      |           |

| 12      | GNDZ      | _    | Analog Ground (bias)                    |           |

| 13      | VSS       | _    | - 5 V Analog Supply Voltage             |           |

| 50      | VDDI      | _    | + 5 V Digital Supply Voltage            |           |

| 49      | GNDI      | _    | Digital Ground                          |           |

## **Interface Pins to MuPP (PEB 31665)**

| 54 | ADU   | 0 | Analog Data Upstream        |  |

|----|-------|---|-----------------------------|--|

| 53 | ADD   | I | Analog Data Downstream      |  |

| 51 | ADCL  | I | Analog Data-Clock           |  |

| 52 | AFSC  | I | Analog Frame-Sync.          |  |

| 48 | ADR   | I | Select odd or even port nr. |  |

| 47 | RESET | I | Interface-Reset             |  |

## **SIEMENS**

Introduction

Table 1 Pin Definition and Functions (PEB 3465) (cont'd)

| Pin No. | Name | Туре | Function | Reference |

|---------|------|------|----------|-----------|

| PIN NO. | Name | туре | Function | Reterence |

## Interface to AHV-SLIC (PEB 4165)

| 71 | IT-A   | 1   | Transversal Current Input (AC+DC), chan. A |  |

|----|--------|-----|--------------------------------------------|--|

| 72 | ITAC-A | 1   | Transversal Current Input (AC), chan. A    |  |

| 73 | VR-A   | 1   | Reference Input, chan. A                   |  |

| 74 | IL-A   | 1   | Longitudinal Current Input, chan. A        |  |

| 77 | ACP-A  | 0   | Two Wire Output Voltage (ACP), chan. A     |  |

| 78 | ACN-A  | 0   | Two Wire Output Voltage (ACN), chan. A     |  |

| 75 | DCP-A  | 0   | Two Wire Output Voltage (DCP), chan. A     |  |

| 76 | DCN-A  | 0   | Two Wire Output Voltage (DCN), chan. A     |  |

| 79 | C1-A   | I/O | Digital Interface to HV-SLIC, chan. A      |  |

| 80 | C2-A   | 0   | Digital Interface to HV-SLIC, chan. A      |  |

| 30 | IT-B   | 1   | Transversal Current Input (AC+DC), chan. B |  |

| 29 | ITAC-B | 1   | Transversal Current Input (AC), chan. B    |  |

| 28 | VR-B   | I   | Reference Input, chan. B                   |  |

| 27 | IL-B   | 1   | Longitudinal Current Input, chan. B        |  |

| 24 | ACP-B  | 0   | Two Wire Output Voltage (ACP), chan. B     |  |

| 23 | ACN-B  | 0   | Two Wire Output Voltage (ACN), chan. B     |  |

| 26 | DCP-B  | 0   | Two Wire Output Voltage (DCP), chan. B     |  |

| 25 | DCN-B  | 0   | Two Wire Output Voltage (DCN), chan. B     |  |

| 22 | C1-B   | I/O | Digital Interface to HV-SLIC, chan. B      |  |

| 21 | C2-B   | 0   | Digital Interface to HV-SLIC, chan. B      |  |

| 31 | IT-C   | I   | Transversal Current Input (AC+DC), chan. C |  |

| 32 | ITAC-C | I   | Transversal Current Input (AC), chan. C    |  |

| 33 | VR-C   | 1   | Reference Input, chan. C                   |  |

| 34 | IL-C   | 1   | Longitudinal Current Input, chan. C        |  |

| 37 | ACP-C  | 0   | Two Wire Output Voltage (ACP), chan. C     |  |

| 38 | ACN-C  | 0   | Two Wire Output Voltage (ACN), chan. C     |  |

| 35 | DCP-C  | 0   | Two Wire Output Voltage (DCP), chan. C     |  |

| 36 | DCN-C  | 0   | Two Wire Output Voltage (DCN), chan. C     |  |

## Table 1 Pin Definition and Functions (PEB 3465) (cont'd)

| Pin No. Name Type | Function | Reference |

|-------------------|----------|-----------|

|-------------------|----------|-----------|

## Interface to AHV-SLIC (PEB 4165) (cont'd)

| 39 | C1-C   | I/O | Digital Interface to HV-SLIC, chan. C      |

|----|--------|-----|--------------------------------------------|

| 40 | C2-C   | 0   | Digital Interface to HV-SLIC, chan. C      |

| 70 | IT-D   | I   | Transversal Current Input (AC+DC), chan. D |

| 69 | ITAC-D | I   | Transversal Current Input (AC), chan. D    |

| 68 | VR-D   | I   | Reference Input, chan. D                   |

| 67 | IL-D   | I   | Longitudinal Current Input, chan. D        |

| 64 | ACP-D  | 0   | Two Wire Output Voltage (ACP), chan. D     |

| 63 | ACN-D  | 0   | Two Wire Output Voltage (ACN), chan. D     |

| 66 | DCP-D  | 0   | Two Wire Output Voltage (DCP), chan. D     |

| 65 | DCN-D  | 0   | Two Wire Output Voltage (DCN), chan. D     |

| 62 | C1-D   | I/O | Digital Interface to HV-SLIC, chan. D      |

| 61 | C2-D   | 0   | Digital Interface to HV-SLIC, chan. D      |

## **SIEMENS**

Introduction

## Table 1 Pin Definition and Functions (PEB 3465) (cont'd)

| Pin No. | Name | Туре | Function | Reference |

|---------|------|------|----------|-----------|

| PIN NO. | Name | туре | Function | Reterence |

### **IO Pins**

| 4  | IO1-A | I/O | User-Programmable I/O Pin, chan. A |

|----|-------|-----|------------------------------------|

| 5  | IO2-A | I/O | User-Programmable I/O Pin, chan. A |

| 6  | I1-A  | 1   | Fixed Input Pin, chan. A           |

| 2  | O1-A  | 0   | Fixed Output Pin, chan. A          |

| 17 | IO1-B | I/O | User-Programmable I/O Pin, chan. B |

| 16 | IO2-B | I/O | User-Programmable I/O Pin, chan. B |

| 15 | I1-B  | I   | Fixed Input Pin, chan. B           |

| 19 | O1-B  | 0   | Fixed Output Pin, chan. B          |

| 44 | IO1-C | I/O | User-Programmable I/O Pin, chan. C |

| 45 | IO2-C | I/O | User-Programmable I/O Pin, chan. C |

| 46 | I1-C  | I   | Fixed Input Pin, chan. C           |

| 42 | O1-C  | 0   | Fixed Output Pin, chan. C          |

| 57 | IO1-D | I/O | User-Programmable I/O Pin, chan. D |

| 56 | IO2-D | I/O | User-Programmable I/O Pin, chan. D |

| 55 | I1-D  | 1   | Fixed Input Pin, chan. D           |

| 59 | O1-D  | 0   | Fixed Output Pin, chan. D          |

|    |       |     |                                    |

## **Miscellaneous Function Pins**

| 14 | RREF | I | External resistor to GNDZ |  |

|----|------|---|---------------------------|--|

| 10 | VA   | I | Voltage sense a           |  |

| 9  | VB   | I | Voltage sense b           |  |

| 8  | VBIM | I | Battery image sense input |  |

### Pins not Used

| 7 | N.C. | _ | Not connected (not used) |  |

|---|------|---|--------------------------|--|

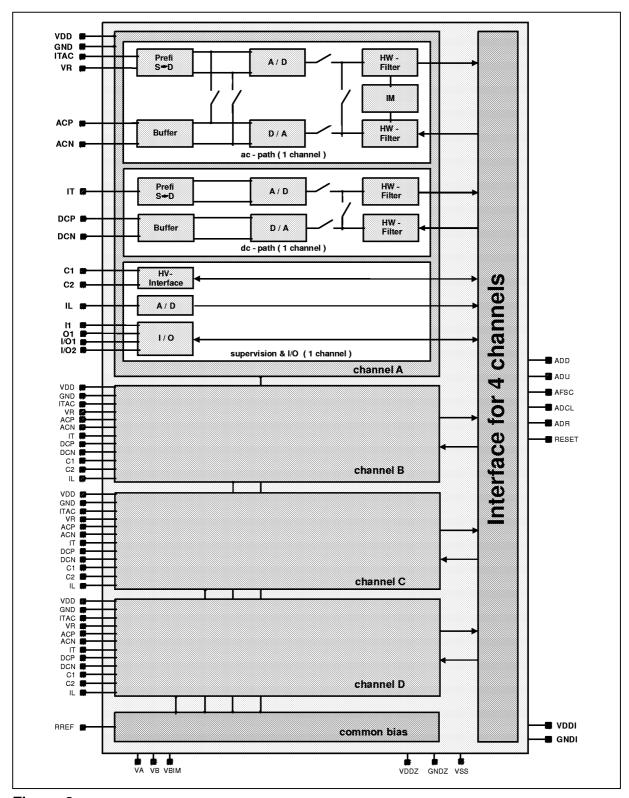

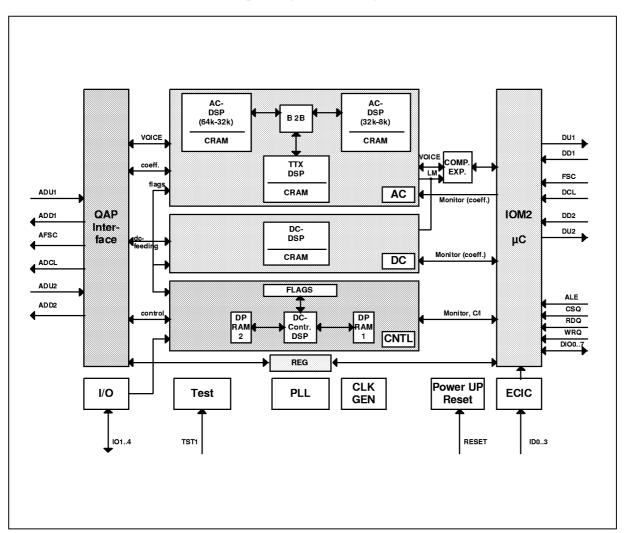

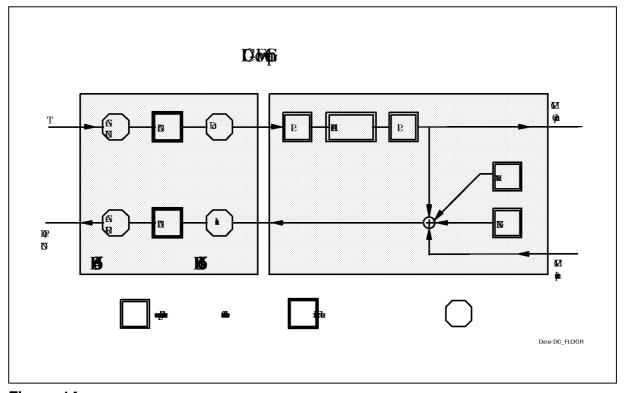

## 1.2.3 Functional Block Diagram (PEB 3465)

Figure 3

04.97

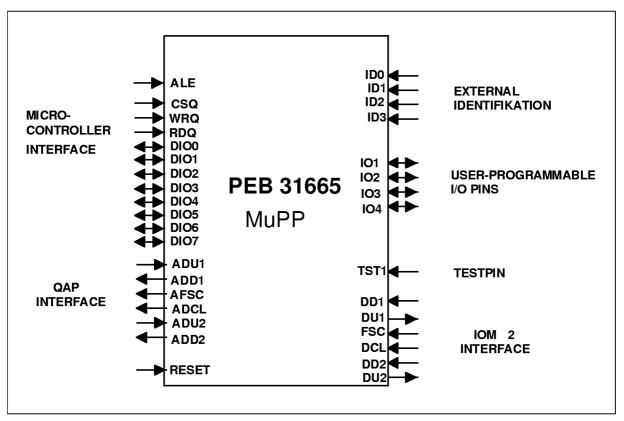

## 1.3 Logic Symbol (PEB 31665)

Figure 4

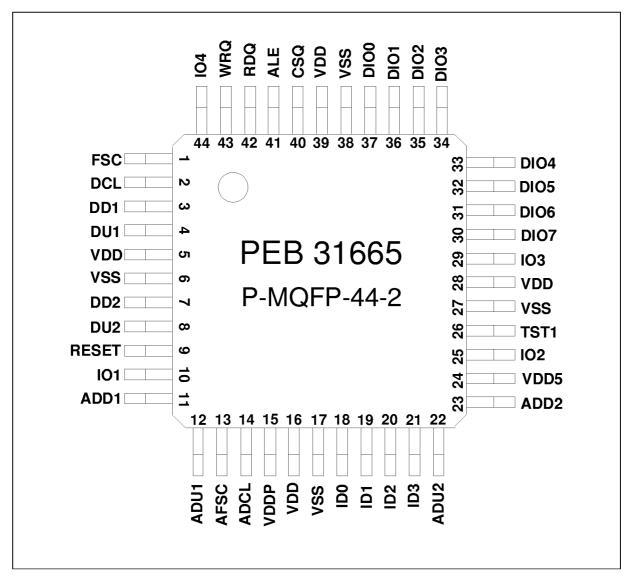

## 1.3.1 Pin Configuration (PEB 31665)

Figure 5

Pin No

Name

Introduction

Reference

## 1.3.2 Pin Definitions and Functions (PEB 31665)

The following tables group the pins according to their functions. They include pin number, pin name, type, a brief description of the function, and cross-references referring to the sections in which the pin functions are discussed.

Table 2 Pin Definitions and Functions (PEB 31665)

Type Function

| FIII NO. | INAIIIE           | Type | Function                               | helefelice |  |  |  |

|----------|-------------------|------|----------------------------------------|------------|--|--|--|

| Power S  | Power Supply Pins |      |                                        |            |  |  |  |

| 6        | VSS               | _    | Digital Ground                         |            |  |  |  |

| 17       | VSS               | _    | Digital Ground                         |            |  |  |  |

| 27       | VSS               | _    | Digital Ground                         |            |  |  |  |

| 38       | VSS               | _    | Digital Ground                         |            |  |  |  |

| 5        | VDD               | _    | + 3.3 V Digital Supply Voltage         |            |  |  |  |

| 15       | VDDP              | _    | + 3.3 V Digital Supply Voltage for PLL |            |  |  |  |

| 16       | VDD               | _    | + 3.3 V Digital Supply Voltage         |            |  |  |  |

| 28       | VDD               | _    | + 3.3 V Digital Supply Voltage         |            |  |  |  |

| 39       | VDD               | _    | + 3.3 V Digital Supply Voltage         |            |  |  |  |

| 24       | VDD5              | _    | + 5 V Digital Supply Voltage           |            |  |  |  |

### IOM®-2 Pins

| 4 | DU1 | 0 | 1'st IOM-2 | Data Upstream (open drain) |  |

|---|-----|---|------------|----------------------------|--|

| 3 | DD1 | 1 | 1'st IOM-2 | Data Downstream            |  |

| 2 | DCL | 1 | IOM-2      | Data-Clock                 |  |

| 1 | FSC | 1 | IOM-2      | Frame-Sync.                |  |

| 8 | DU2 | 0 | 2'nd IOM-2 | Data Upstream (open drain) |  |

| 7 | DD2 | I | 2'nd IOM-2 | Data Downstream            |  |

## **SIEMENS**

Introduction

Table 2 Pin Definitions and Functions (PEB 31665) (cont'd)

| Pin No. N | Name Type | Function | Reference |

|-----------|-----------|----------|-----------|

|-----------|-----------|----------|-----------|

### MuPP/QAP Interface

| 11 | ADD1 | 0 | 1'st QAP | Data Downstream |  |

|----|------|---|----------|-----------------|--|

| 12 | ADU1 | I | 1'st QAP | Data Upstream   |  |

| 13 | AFSC | 0 | QAP      | Frame-Sync      |  |

| 14 | ADCL | 0 | QAP      | Data-Clock      |  |

| 23 | ADD2 | 0 | 2'nd QAP | Data Downstream |  |

| 22 | ADU2 | I | 2'nd QAP | Data Upstream   |  |

### Microcontroller Interface

| 40 | CSQ  | 1   | μC Chip select          |  |

|----|------|-----|-------------------------|--|

| 41 | ALE  | I   | μC Address latch enable |  |

| 42 | RDQ  | I   | μC Data-Clock read      |  |

| 43 | WRQ  | I   | μC Data-Clock write     |  |

| 37 | DIO0 | I/O | μC Data / Address       |  |

| 36 | DIO1 | I/O | μC Data / Address       |  |

| 35 | DIO2 | I/O | μC Data / Address       |  |

| 34 | DIO3 | I/O | μC Data / Address       |  |

| 33 | DIO4 | I/O | μC Data / Address       |  |

| 32 | DIO5 | I/O | μC Data / Address       |  |

| 31 | DIO6 | I/O | μC Data / Address       |  |

| 30 | DIO7 | I/O | μC Data / Address       |  |

### **IO Pins**

| 10 | IO1 | I/O | User-Programmable I/O Pin |  |

|----|-----|-----|---------------------------|--|

| 25 | IO2 | I/O | User-Programmable I/O Pin |  |

| 29 | IO3 | I/O | User-Programmable I/O Pin |  |

| 44 | IO4 | I/O | User-Programmable I/O Pin |  |

## **SIEMENS**

## Introduction

## Table 2 Pin Definitions and Functions (PEB 31665) (cont'd)

| Pin No. | Name | Туре | Function | Reference |

|---------|------|------|----------|-----------|

|---------|------|------|----------|-----------|

### **Miscellaneous Function Pins**

| 9  | RESET | 1 | Reset                               |  |

|----|-------|---|-------------------------------------|--|

| 18 | ID0   | I | External Identification             |  |

| 19 | ID1   | I | External Identification             |  |

| 20 | ID2   | 1 | External Identification             |  |

| 21 | ID3   | 1 | External Identification             |  |

| 26 | TST1  | I | Test Pin (must be connected to VSS) |  |

## 1.3.3 Functional Block Diagram (PEB 31665)

Figure 6

04.97

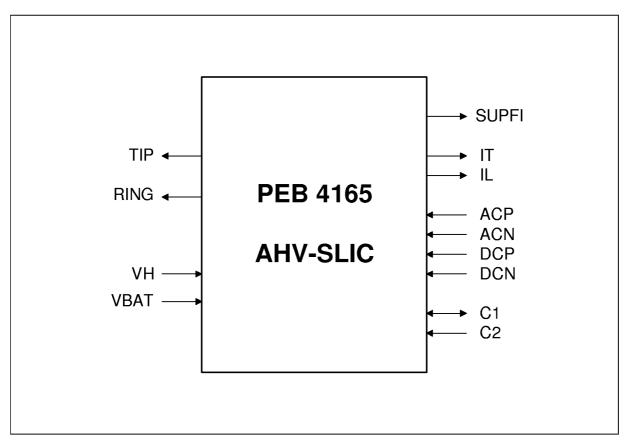

## 1.4 Logic Symbol (PEB 4165)

Figure 7

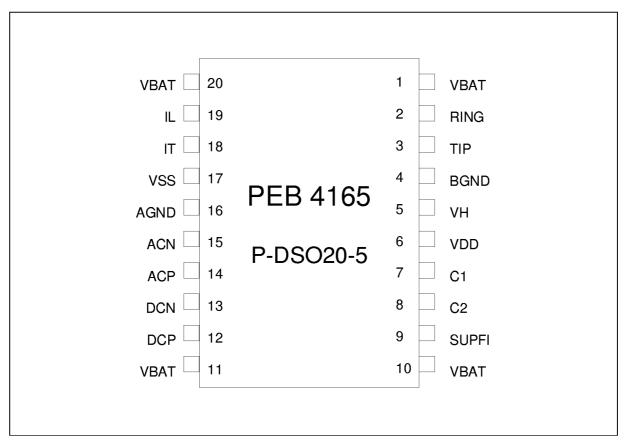

## 1.4.1 Pin Configuration (PEB 4165)

Figure 8

## 1.4.2 Pin Definitions and Functions (PEB 4165)

| Pin No.        | Symbol  | Type   | Description                                                                                                                                        |  |

|----------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1,10,11,<br>20 | VBAT    | Supply | Negative battery supply voltage (- 24 80 V), referred to BGND                                                                                      |  |

| 2              | RING    | 0      | Subscriber loop connection RING                                                                                                                    |  |

| 3              | TIP     | 0      | Subscriber loop connection TIP                                                                                                                     |  |

| 4              | BGND    | Supply | Battery ground: TIP, RING, VBAT and VH refer to this pin                                                                                           |  |

| 5              | VH      | Supply | Auxiliary positive battery supply voltage (+ 5 + 85 V) used in ringing mode                                                                        |  |

| 9              | SUPFI   | 0      | External capacitance for supply voltage filtering (internal resistance of about 30 $\mbox{k}\Omega)$                                               |  |

| 6              | VDD     | Supply | Positive supply voltage (+ 5 V), referred to AGND                                                                                                  |  |

| 7              | C1      | I/O    | Ternary logic input, controlling the operation mode; i case of thermal overload this pin sinks a current of ty 150 μA                              |  |

| 8              | C2      | I      | Ternary logic input, controlling the operation mode                                                                                                |  |

| 12,13          | DCP,DCN | I      | Differential two wire DC-input voltage; multiplied by – 25 and related to (VH – VBAT) / 2, DCN appears at TIP and DCP at RING output, respectively |  |

| 14,15          | ACP,ACN | I      | Differential two wire AC-input voltage; multiplied by – 3.125, ACN appears at TIP and ACP at RING output, respectively                             |  |

| 16             | AGND    | Supply | Analog ground: VDD, VSS and all signal and control pins with the exception of TIP and RING refer to AGND                                           |  |

| 17             | VSS     | Supply | Negative supply voltage (-5 V), referred to AGND                                                                                                   |  |

| 18             | IT      | 0      | Current output representing the transversal current scaled down by a factor of 50.                                                                 |  |

| 19             | IL      | 0      | Current output: longitudinal line current scaled down by a factor of 50.                                                                           |  |

04.97

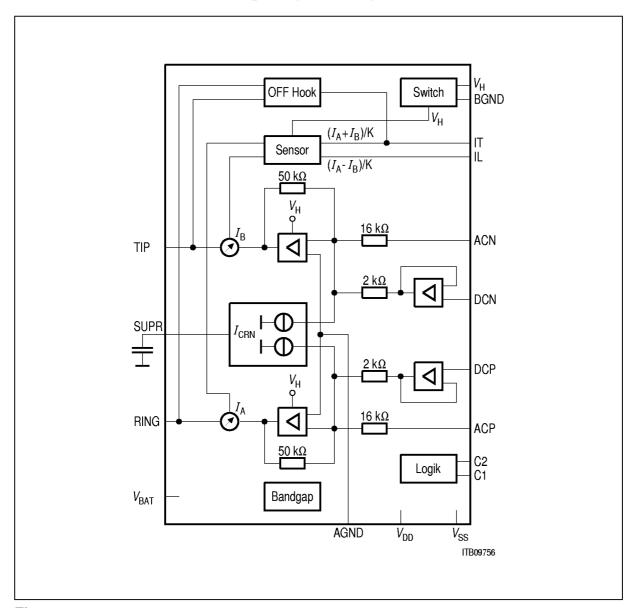

## 1.4.3 Functional Block Diagram (PEB 4165)

Figure 9

## 1.5 System Integration

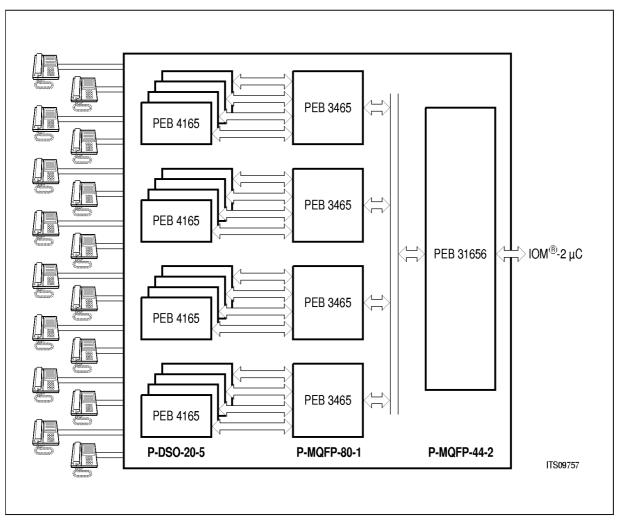

Figure 10 Block Figure of an Analog Linecard for 16 Subscribers Using MuSLIC

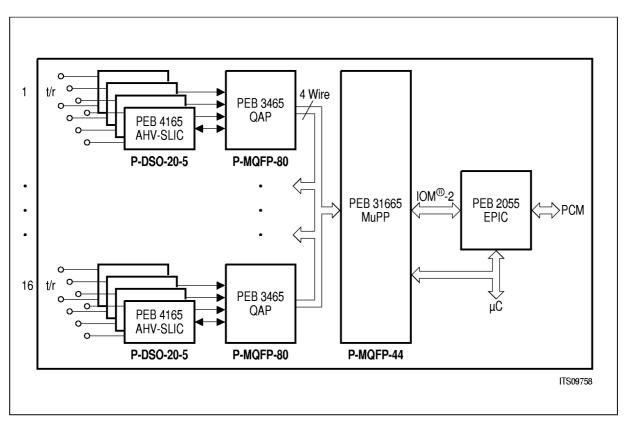

Figure 11 Application Example of a Central Office Analog Linecard for 16 Subscribers

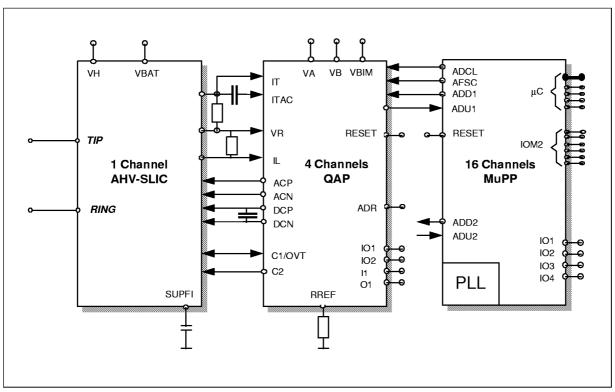

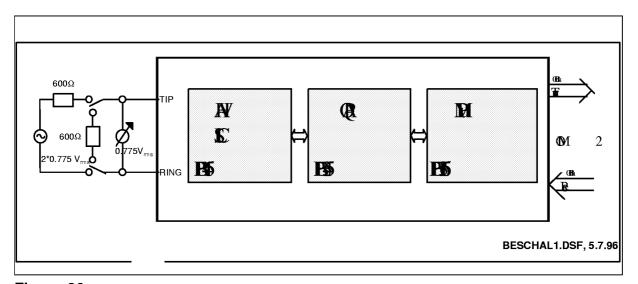

Figure 12 Overview of the Connection of MuPP, QAP and AHV-SLIC for One Subscriber

### 2 Functional Description

The Multichannel Signal Processing Subscriber Line Interface Codec Filter Chipset, MuSLIC, is a logic continuation of the well established family of the SIEMENS PCM-Codec-Filter-ICs with the integration of all DC-feeding, Supervision and Meterpulse Injection features on chip as well. Fabricated in advanced CMOS, BiCMOS and High Voltage Technology SPT170 the MuSLIC is tailored for very flexible solutions in analog/digital communication systems.

The chip set consists of the digital signal processor for 16 channels (MuPP, multichannel processor for POTS), the analog/digital and digital/analog converter for 4 channels (QAP, quad analog POTS) and the high voltage interface chip for 1 channel (AHV-SLIC, advanced high voltage subscriber line interface circuit).

The MuPP uses the benefits of a DSP not only for the voice channel but even for line feeding and supervision which leads to a very high flexibility without the need of external components. Based on an advanced digital filter concept, the PEB 31665 (MuPP) and the PEB 3465 (QAP) provides excellent transmission performance. The new filter concept leads to a maximum of independence between the different filter blocks. Each filter block can be seen as a one to one representative of the corresponding network element. Together with the software package MuSLICOS, filter optimizing to different applications can be done in a clear and straight forward procedure. The AC frequency behavior is mainly determined by the digital filters. Using the oversampling 1 bit  $\Sigma\Delta$ -AD/DA converters, linearity is only limited by second order parasitic effects.

The digital solution of line feeding offers free programmability of feeding current and voltage as well as very fast settling of the dc-operating point after transitions. A 0.3 Hz lowpass filter in the DC-loop is mainly responsible for the system stability.

Additionally teletax generation and filtering is implemented as well as free programmable balanced ring generation with zero-crossing injection. Offhook detection with programmable thresholds is possible in all operating modes. To reduce overall power consumption of the linecard, the MuPP, the QAP and the AHV-SLIC provide a Power Down mode.

To program the MuSLIC or to get status information about the chipset or the system 2 user interfaces are available: the IOM-2 interface and a 8-bit-parallel simple microcontroller interface.

The PEB 4165 (AHV-SLIC) provides battery feeding between -24 V and -80 V and ringing injection with a differential ring voltage up to 85 Vrms. In order to achieve these high amplitudes, an auxiliary positive battery voltage is used during ringing. This voltage can also be applied to drive very long telephone lines.

The AHV-SLIC is designed for a voltage feeding - current sensing line interface concept and provides sensing of transversal and longitudinal currents on both wires. In Power Down mode the AHV-SLIC is switched off turning the line outputs to a high impedance state. Off-hook supervision is provided by activating a simple line current sensor.

### 2.1 Principles

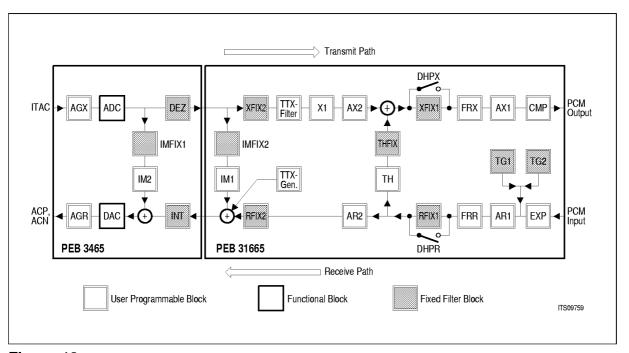

### 2.1.1 Signal Flow Graph: AC

Figure 13

#### **Transmit Path**

The analog input signal has to be connected to pin ITAC of the PEB 3465 by an external capacitor (470 nF) for AC/DC separation. After passing a programmable gain stage (AGX = 0 or 6 dB) and a simple antialiasing prefilter the voice signal is converted to a 1-bit digital data stream in the  $\Sigma\Delta$ -converter. The first down sampling steps are done in fast running digital hardware filters on the PEB 3465. This down sampled AC-signal (64 kHz sampling rate) is sent to the PEB 31665 via the MuPP/QAP-Interface in the ADU-channel. The following signal processing is done in the DSP-machine of the PEB 31665. The benefits of this are the programmability of frequency and gain behavior. At the end the fully processed signal is transferred to the IOM-2 Interface in a PCM-compressed (A-law /  $\mu$ -law) signal representation.

#### **Receive Path**

The digital input signal is received via the IOM-2 Interface of the PEB 31665. Expansion, PCM-lowpass-filtering, gain correction and frequency response correction are the next steps which are done by the DSP-machine. This 64 kHz AC signal is sent from the QAP to the MuPP via the MuPP/QAP-Interface in the ADD-channel. The up sampling interpolation steps are processed by fast hardware structures in the PEB 3465 to reduce the DSP-workload. The 1-bit data stream is then converted to an analog equivalent. A subsequent programmable gain stage (AGR = 0 or 6 dB) and smoothing filter provides the AC output signal at the Pins ACP and ACN of the PEB 3465 for direct connection to the AHV-SLIC PEB 4165.

### Loops

There are two different loops implemented: The Impedance Matching (IM) loop which is divided into 2 separate loops to guarantee very high flexibility to various impedances, and the Transhybrid Balancing (TH) loop.

For test purposes it is possible to close a loop behind the  $\Sigma\Delta$ -converter to check either the analog of the digital part of the PEB 3465 and the PEB 31665 respectively.

### 2.1.2 Signal Flow Graph: DC

Figure 14

### **DC Characteristic**

The incoming information (transmit direction) at pin IT (scaled transversal AC + DC-current, transferred to a voltage via an external 1.5 k $\Omega$  resistor at IT) passes first an antialiasing filter and is then converted to a 1-bit digital data stream in the  $\Sigma\Delta$ -converter. Down sampling is done in hardware filters of the PEB 3465. This DC-information (2 kHz sampling rate) is then fed to the PEB 31665 where it is first lowpass filtered (0.3 Hz corner frequency) for stability and noise reasons. The following DC-characteristic consists of three branches which represents different kinds of feeding behavior. In typical applications it acts as a programmable constant current source  $(R_{\rm in} > 30 \text{ k}\Omega)$ . If the desired value cannot be held feeding switches automatically and smoothly to the resistive branch ( $R_{\rm in}$  programmable between 0 ... 1 k $\Omega$ ). The third branch is used for feeding long lines - the DC-characteristic switches to a constant voltage behavior. For superimposing voice as well as Teletax pulses the necessary drop at the line can be calculated and taken into account as well. The outgoing bit stream (2 kHz sampling rate), representing the DC-feeding value is then sent back to the PEB 3465 where a 1-bit  $\Sigma\Delta$ -converter and a following smoothing filter (using an external 33 nF capacitor) establish the desired values at the Pins DCP and DCN, respectively. Depending on the operating mode (Active, Ringing, Active with Boosted Battery) a gain of 0 or 4 dB is inserted.

For test purposes it is possible to close a loop to test either the analog part or the digital part of the DC path.

## Supervision

The HOOK-information is the most important one and is provided via the IOM-2 Interface (CIDU-4: HOOK; see **chapter 4.2**), in all operating modes:

Power Down: In this state the transversal line current is sensed by the PEB 4165

and fed to the PEB 3465 via Pin IT. Offhook is detected if the voltage

at IT exceeds a programmed value.

Active: Offhook is detected if the incoming voltage at IT exceeds a

programmed value. To avoid instable information, lowpass filtering

and a hysteresis is provided.

Ringing: Offhook is detected if the DC-value at IT exceeds the programmed

Ring Trip threshold. The AC-value is filtered automatically. Ring Trip detection is reported within 2 cycles of the ring period and then the internal ring generator is switched off within 2 cycles at zero

crossing of the ring voltage.

For Ground Key information the PEB 4165 provides the longitudinal current information at the Pin IL. The PEB 3465 uses a  $\Sigma\Delta$ -converter - similar to the DC-transmit path - to convert this signal to its digital representation. The accuracy is  $\pm$  10% compared to  $\pm$  5% of the DC-path. The 1-bit digital data stream is also down sampled and sent to the

PEB 31665 via the ADU-channel of the MuPP/QAP-Interface. Generation of the Ground Key bit is done in the PEB 31665 (CIDU-3: GNK; see **chapter 4.2**)

#### **Additional Features**

The PEB 3465 provides three general purpose input Pins (VA, VB, VBIM) for measuring. Via the MuPP/QAP-Interface it is possible to select one of these inputs for the measurement. The DC-signal at the selected input is converted to digital using the same  $\Sigma\Delta$ -converter as for Ground Key information (accuracy of  $\pm$  10%) and sent to the PEB 31665. The input range is between -2.4 V ... +2.4 V. As a further selection it is also possible to measure the internal VDDZ-voltage of the PEB 3465.

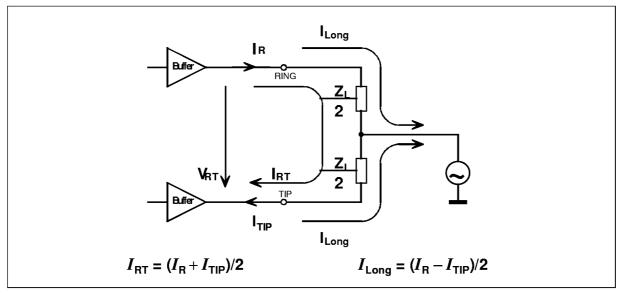

#### 2.1.3 AHV-SLIC

The Advanced High Voltage Subscriber Line IC (AHV-SLIC) PEB 4165 is a reliable interface between the telephone line and the PEB 3465/PEB 31665.

The PEB 4165 supports AC and DC control loops based on feeding a voltage  $V_{\rm RT}$  to the line and sensing the transversal line current  $I_{\rm RT}$  (**figure 15**).

DC- and AC-voltages are handled separately with different gain on the AHV-SLIC. Both are applied differentially via pins DCP, DCN, and ACP, ACN, respectively. The line voltages  $V_{\rm R}$  and  $V_{\rm T}$  are the amplified input voltages, related to the mean supply voltage,  $V_{\rm T} = {\rm VTIP} = ({\rm VH'-VBAT}) / 2 - 25 \times {\rm VDCN} - 50/16 \times {\rm VACN}$

$$V_{\rm R}$$

= VRING = (VH' – VBAT) / 2 – 25 × VDCP – 50/16 × VACP.

Depending on the operation mode, VH' is switched either to VH or to BGND via the supply switch. The transversal line voltage  $V_{\rm RT}$  =  $V_{\rm R}$  –  $V_{\rm T}$  is simply related to the input voltages

$$V_{\mathsf{RT}}$$

= 25 × (VDCP - VDCN) + 50/16 × (VACP - VACN) = 50 × VDCP + 6.25 × VACP

A reversed polarity of  $V_{\rm RT}$  is easily obtained by changing the sign of (VDCP – VDCN).

The transversal and longitudinal currents are measured in the buffers and scaled images are provided at the IT and IL pin, respectively:

IT=

$$(I_{R} + I_{TIP})/100 = I_{RT}/50$$

IL =  $-(I_{R} - I_{TIP})/100 = -I_{Long}/50$

04.97

Figure 15 Definition of Output Current Directions

The PEB 4165 operates in four modes controlled by ternary logic signals at the C1 and C2 input (see **table 3**).

**Table 3** Programming of Operating Modes

|            |     |      | C 2 (Pin 9) |      |  |

|------------|-----|------|-------------|------|--|

|            |     | VIL  | VIM         | VIH  |  |

|            | VIL | PDNH | PDNR        | HIR  |  |

| C 1(Pin 8) | VIM | PDNH | ВВ          | HIT  |  |

|            | VIH | PDNH | ACT         | HIRT |  |

HIR ... Ring wire set to high impedance

HIT ... Tip wire set to high impedance

**High Impedance (HIR/HIT/HIRT):** In this mode each of the line outputs can be programmed to show high impedance. HIT switches off the TIP buffer, while the current through the RING output still can be measured by IT or IL. Programming HIR switches off the RING buffer. In the mode HIRT both buffers show high impedance.

**Active (ACT):** This is the regular transmit and receive mode for voiceband and teletax. The line driving section is operated between VBAT and BGND.

**Boosted battery (BB):** In order to provide a balanced ring signal of up to 85 Vrms or to drive longer telephone lines, an auxiliary positive battery voltage VH is used, enabling a higher voltage across the line. Transmission performance remains unchanged compared with ACT mode.

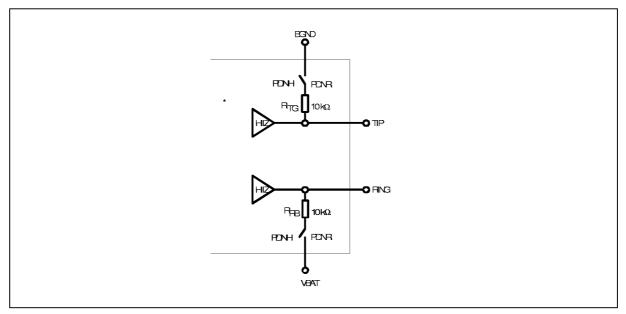

**The Power Down (PDN)** state is intended to reduce power consumption of the linecard to a minimum: the PEB 4165 is switched off completely, no operation is available.

With respect to the output impedance of TIP and RING two PDN-modes have to be distinguished:

A resistive one (PDNR) provides a connection of 10  $k\Omega$  each from TIP to BGND and RING to VBAT, respectively, while the outputs of the buffers show high impedance (**figure 16**). The current through these resistors is sensed and transferred to the IT pin to allow offhook supervision.

The other mode (PDNH) offers high impedance at TIP and RING.

Figure 16 TIP and RING Impedance in Power Down

### 2.1.4 Test Features

There are two different kinds of test features: Internal test loops for circuit testing and defined test loops to perform board and line tests. There are loops for testing AC and DC path. As a special feature it is possible to switch signals to and from the DC-path via the IOM-2 Interface. Additionally there is the possibility to cut off the AC-receive and transmit path (the different kinds of testmodes are described in **chapter 8**).

04.97

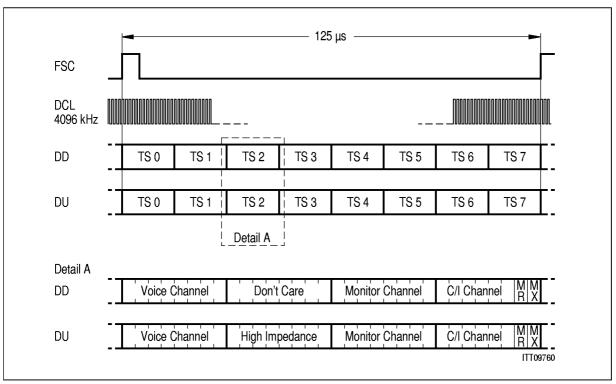

### 3 Interfaces

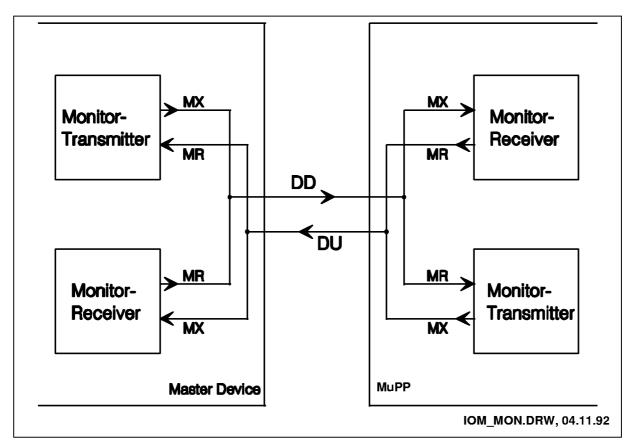

### 3.1 IOM<sup>®</sup>-2 Interface

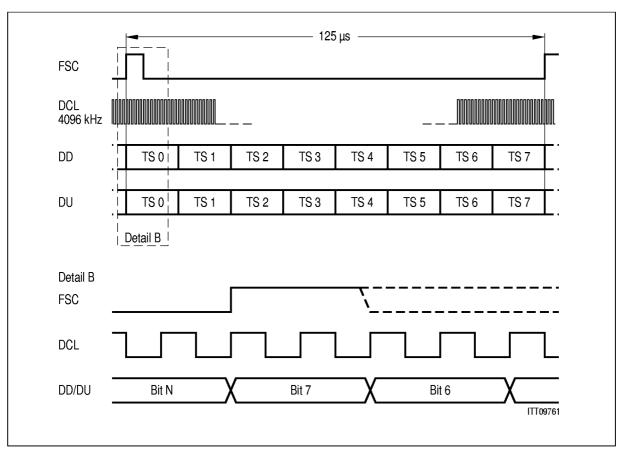

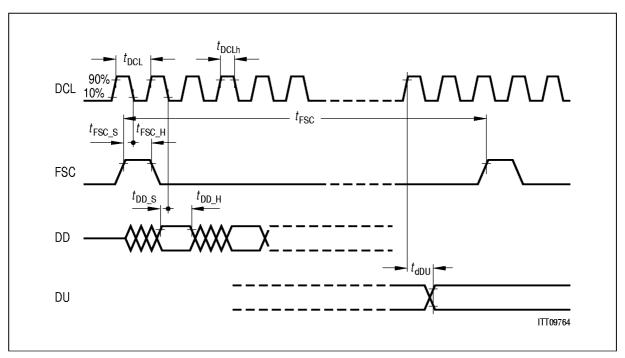

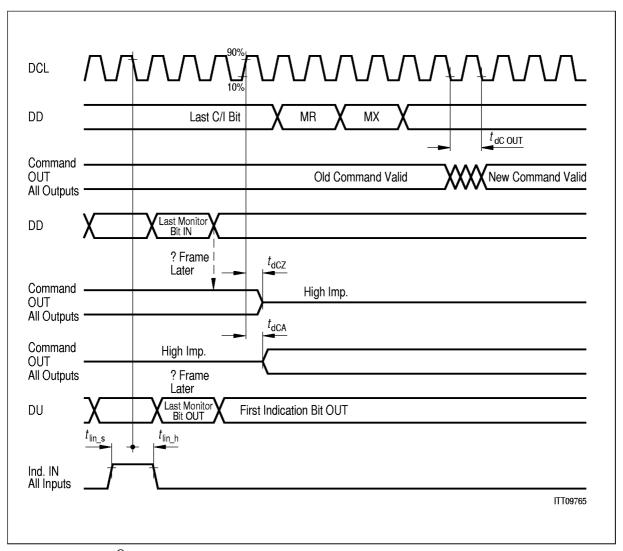

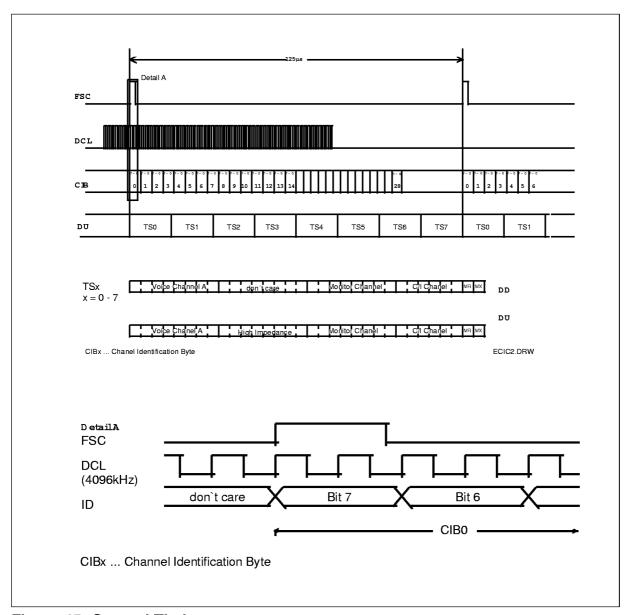

The IOM-2 Interface consists of two data lines and two clock lines. DU (data upstream) carries data from the MuSLIC to a master device. DD (data downstream) carries data from the master device to the MuSLIC. A frame synchronization clock signal (8 kHz, FSC) as well as a data clock signal (4096 kHz, DCL) has to be supplied to the MuSLIC. The MuSLIC handles data as described in the IOM-2 specification for analog devices (see **chapter 10.1**).

Figure 17 IOM®-2 Interface Timing for 8 Voice Channels (per 8 kHz frame)

Figure 18 IOM®-2 Interface Timing (DCL = 4096 kHz, per 8 kHz frame)

04.97

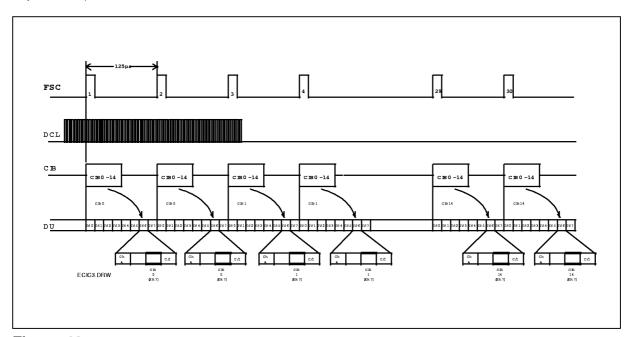

## IOM®-2 Time Slot Assignment

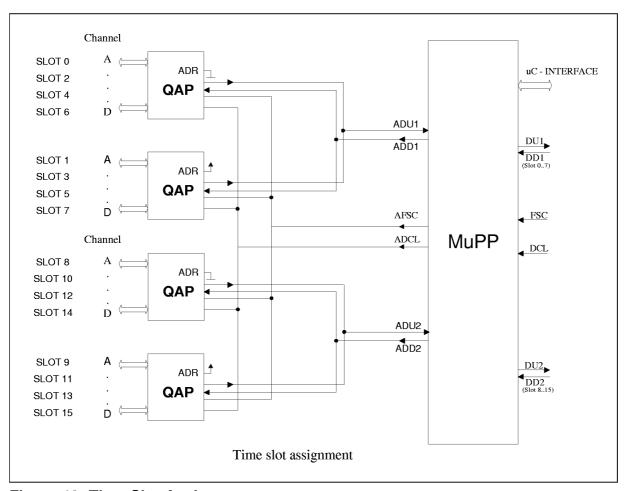

An assignment of 16 time slots is given by the two IOM-2 interfaces of the MuPP. Each of them assigns 8 time slots synchronized with the FSC. This 8 slot structure is carried on from the MuPP to the QAP. In the QAP the assignment is partly done by pin-strapping (see **figure 19**).

Figure 19 Time Slot Assignment

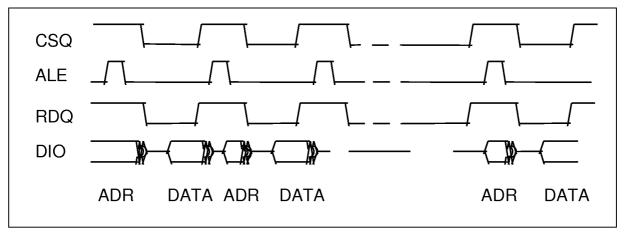

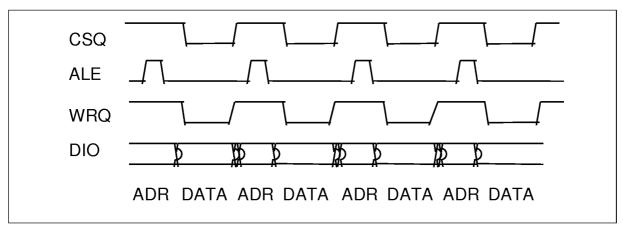

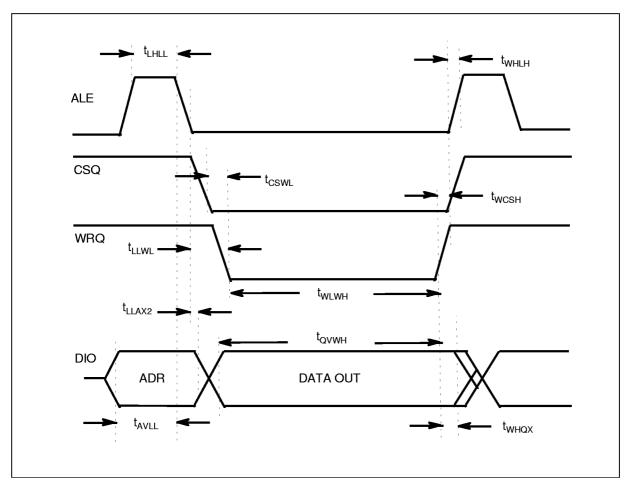

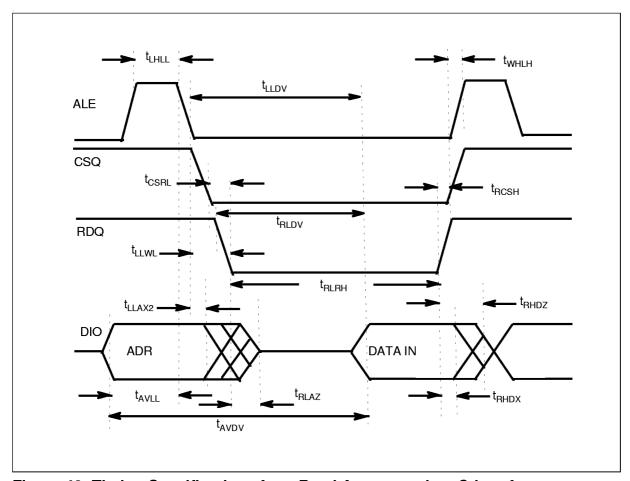

### 3.2 $\mu$ C Interface

The parallel  $\mu$ C-Interface is used to communicate with an external master device and consists of four control lines (ALE, CSQ, RDQ, WRQ) and 8 bidirectional data lines (DIO0 ... DIO7) and provides fast parallel data transfer to a microcontroller device as an alternative to the IOM-2 monitor channel data transfer. Only one method of transfer can be used at a time, with the  $\mu$ C-Interface having a higher priority than the IOM-2 Interface. Thus, data transfer via the  $\mu$ C-Interface interrupts a communication via the IOM-2 monitor channel. During a data transfer cycle via the  $\mu$ C-Interface, IOM-2 monitor channel data will be ignored. The C/I-channel information is still transferred via the C/I-channel of the IOM-2 interface and is not affected by the  $\mu$ C-Interface communication.

The  $\mu$ C-Interface of the MuPP has a multiplexed 8-bit address/data bus and allows direct connection to a microcontroller of the 8051- and the Siemens C16X-family without additional components.

With every falling edge of ALE-line the MuPP latches the bus data on the 8 data lines DIO0 ... DIO7 and stores it as address information. CSQ combined with RDQ or WRQ starts the data transfer cycle via the parallel  $\mu$ C-Interface. The data on DIO0 ... DIO7 are valid on the rising edge of WRQ/RDQ (if CSQ is low). Depending on the previously latched address information, these data have a different meaning; e.g. the 8 bit of a command/data byte is preceded by the address 00000001 or the subscriber/slot address for a subsequent data byte of a e.g. SOP-, TOP-, or COPI-command has the address information 00000000 (see **table 4**).

A data transfer cycle to address 00000000 and 111111111 is already finished after the transfer of the first data byte; transfer cycles to addresses 00000001 and 00000010 consists of more transfers, depending on the length information in the first byte.

As soon as the data transfer cycle via the  $\mu$ C-Interface has been completed, control information via the IOM-2 monitor channel will be accepted again (synchronized with the next FSC), until the next data transfer cycle starts with CSQ and RDQ/WRQ.

Figure 20 Example for a Read Access, with One Data Byte Transferred via DIO

Figure 21 Example for a Write Access, With One Data Byte Transferred

Table 4 Possible Address Information to Identify the Following Data Nibbles

| Address  | Command            |

|----------|--------------------|

| 00000000 | address            |

| 0000001  | data               |

| 0000010  | status             |

|          | reserved           |

| 11111111 | reset μC Interface |

Data transfer to and from the MuSLIC is asynchron and the data will be transferred in bytes. Basically there is no difference to the IOM-2 commands, accept those which requires a slot specific address information.

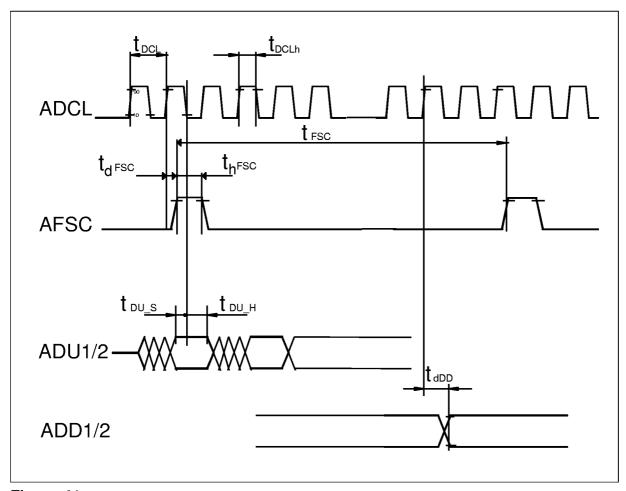

### 3.3 MuPP/QAP Interface

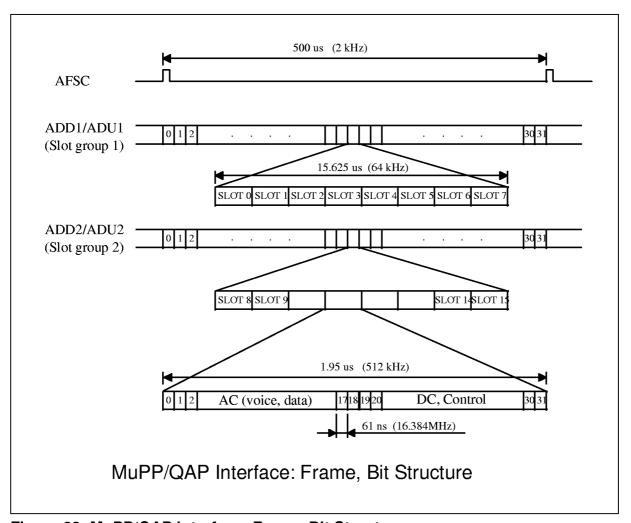

The MuPP/QAP-Interface, the link between the MuPP and the QAP, is a serial interface based on the 6 signals AFSC (analog frame sync), ADCL (analog data clock), ADU1/ADU2 (analog data upstream) and ADD1/ADD2 (analog data downstream). ADU1 and ADD1 are common to the first group of 8 time slots (channels) and ADU2 and ADD2 to the second 8 time slots (channels). AFSC and ADCL are common to both groups of time slots (timing diagram see **chapter 7.2.6**).

Figure 22 MuPP/QAP Interface: Frame, Bit Structure

**Interfaces**

#### 3.4 QAP/AHV-SLIC Interface

#### **Output Voltage AC (ACP, ACN)**

The output voltage at the pins ACP and ACN represents the AC-information together with Teletax info at the receive path. The AC-information is received via the MuPP/QAP-Interface in the ADD channel. The 64-kHz Bitstream is converted to analog, passes a programmable gain stage of 0 / - 6 dB and is buffered to drive a load of  $R_{\rm I} > 15$  k $\Omega$  and  $C_{\rm I} < 10$  pF, which is the input impedance of the AHV-SLIC.

### **Output Voltage DC (DCP, DCN)**

The output voltage at the pins DCP and DCN represents the DC-information together with the Ring Burst at the receive path. The DC-information is received via the MuPP/QAP-Interface in the ADD channel. The 2-kHz Bitstream is converted to analog and buffered to drive an external smoothing capacitor of 33 nF. The pins are directly connected to the AHV-SLIC.

#### Transversal Current Sense AC - Input (ITAC)

The pin ITAC is the input voltage pin for the AC transversal current information from the AHV-SLIC in the transmit path. AC/DC separation is done by an external highpass filter (ext. capacitor = 470 nF). The input resistance is larger than 20 k $\Omega$ . Current/voltage conversion is done via an external resistor of 1.5 k $\Omega$  (same for pin IT). The signal passes a programmable gain stage 0 or 6 dB, is converted to digital and sent to the PEB 31665 via the MuPP/QAP-Interface in the ADU channel (64-kHz Bitstream).

#### Transversal Current Sense DC - Input (IT)

The pin IT is the input voltage pin for the DC transversal current information from the AHV-SLIC in the transmit path. The input resistance is larger than 500 k $\Omega$ . Current/voltage conversion is done via an external resistor of 1.5 k $\Omega$  (same for pin ITAC). The voltage at Pin IT is lowpass filtered and converted to digital. The bitstream (2 kHz) is sent to the PEB 31665 via the MuPP/QAP-Interface for further signal processing.

### **Longitudinal Current Sense - Input (IL)**

The scaled longitudinal current information transferred from the AHV-SLIC - the current/voltage conversion is done by an external resistor of 1.5 k $\Omega$  - is converted into digital and sent to the PEB 31665 via the MuPP/QAP-Interface in the ADU channel. In the PEB 31665 the IL-information is lowpass filtered (time programmable using DUPGNK-counter) and reported via the Data Upstream C/I-channel (CIDU-3) of the IOM-2 interface if the measured value exceeds a programmed limit. In Power Down, the GNK-bit is set to "0" and the setting of the Interrupt bit (CIDU-3) caused by GNK is prohibited.

Interfaces

### Ternary Interface (C1, C2)

In order to set the AHV-SLIC to the different operating modes, the information of the board-controller is passed through from the IOM-2-channel via the MuPP/QAP-Interface to the ternary AHV-SLIC-Interface pins C1 and C2.

#### Table 5

|    |     | C2   |      |      |  |  |

|----|-----|------|------|------|--|--|

|    |     | VOL  | VOM  | VOH  |  |  |

|    | VOL | PDNH | PDNR | HIR  |  |  |

| C1 | VOM | ACT2 | ВВ   | HIT  |  |  |

|    | VOH | ACT3 | ACT  | HIRT |  |  |

PNDH - Power Down High Impedance

PDNR - Power Down Resistive

ACT - Active Mode

ACT2 - Active Mode 2 (power save for SLIC, for future use)

ACT3 - Active Mode 3 (power save for SLIC, for future use)

BB - Boosted Battery

HIR - Ring wire set to high impedanceHIT - Tip wire set to high impedance

HIRT - Ring and Tip wires set to high impedance

For signalling "Over temperature" the AHV-SLIC drains a current (IOT) from pin C1. This current is sensed by the PEB 3465 and transferred in the ADU channel to the PEB 31665. The PEB 31665 sends the overtemperature message via the C/I-channel (CIDU-2: SLCX and TCR0-5) of the IOM-2 Interface. This is possible in any operating states of the AHV-Interface except for Power Down.

#### 4 Programming the MuSLIC

With the appropriate commands, the MuSLIC can be programmed and verified very flexible via the IOM-2 Interface Monitor channel, and the Microcontroller Interface respectively.

#### Transfer via the IOM®-2 Interface

Data transfer to the MuSLIC starts with a MuSLIC-specific address byte (81<sub>H</sub>).

With the second byte one of 5 different types of commands (SOP, TOP, XOP, COP or COPI) is selected. Due to the extended MuSLIC feature control facilities these commands contain additional information (e.g. number of subsequent bytes) for programming (write) and verifying (read) the MuSLIC status.

A write command is followed by up to 8 bytes of data. The MuSLIC responds to a read command with its IOM-2 specific address and the requested information, that is up to 15 bytes of data.

**Attention:** Each byte of the monitor channel has to be transferred twice at least according to the IOM-2 Monitor handshake procedure. (For more information on IOM-2 specific Monitor Channel Data Structure see **chapter 3.1** and **chapter 10**).

#### Transfer via the Microcontroller Interface

Data transfer to and from the MuSLIC is asynchron and the data will be transferred in bytes. Basically there is no difference to the IOM-2 commands.

(For more information, about the  $\mu$ C Interface see **chapter 3.2**).

#### 4.1 Types of Monitor / $\mu$ C Interface Bytes

The 8-bit Monitor /  $\mu$ C Interface bytes have to be interpreted as either commands or status information stored in Configuration Registers or the Coefficient RAMs. There are 5 different types of MuSLIC commands which are selected by bit 4 and 5 (partly bit 2 and 3) as shown below.

| SOP                                      |   | STA | ATUS OP | ERATION: |   | MuSLIC status setting/monitoring |       |       |       |  |

|------------------------------------------|---|-----|---------|----------|---|----------------------------------|-------|-------|-------|--|

| Bit                                      | 7 |     | 6       | 5        | 4 | 3                                | 2     | 1     | 0     |  |

|                                          |   | В   | RW      | 0        | 1 | ATR                              | LSEL2 | LSEL1 | LSEL0 |  |

| XOP EXTENDED OPERATION: General settings |   |     |         |          |   |                                  |       |       |       |  |

| Bit                                      | 7 |     | 6       | 5        | 4 | 3                                | 2     | 1     | 0     |  |

|                                          |   | 0   | RW      | 1        | 0 | ATR                              | LSEL2 | LSEL1 | LSEL0 |  |

|                                                                                       |       |          |         |     |         | Progra       | mming th    | e MuSLIC |  |  |  |

|---------------------------------------------------------------------------------------|-------|----------|---------|-----|---------|--------------|-------------|----------|--|--|--|

| TOP                                                                                   | TRA   | ANSFER ( | PERATIO | ON: | Read Ce | ertain Statu | ıs / Option | s only   |  |  |  |

| Bit                                                                                   | 7     | 6        | 5       | 4   | 3       | 2            | 1           | 0        |  |  |  |

|                                                                                       | 0     | R        | 1       | 1   | 0       | 0            | LSEL1       | LSEL0    |  |  |  |

| COP COEFFICIENT OPERATION: Filter coefficient setting/monitoring  Bit 7 6 5 4 3 2 1 0 |       |          |         |     |         |              |             | _        |  |  |  |

|                                                                                       | ICRAM | RW       | 0       | 0   | 0       | 1            | WCRAM1      | WCRAM0   |  |  |  |

| COPI COEFFICIENT OPERATION INITIALIZE: Coefficient set assignment                     |       |          |         |     |         |              |             |          |  |  |  |

| Bit                                                                                   | 7     | 6        | 5       | 4   | 3       | 2            | 1           | 0        |  |  |  |

|                                                                                       | В     | RW       | 0       | 0   | 1       | 0            | LSEL1       | LSEL0    |  |  |  |

# Table 6 Storage of Programming Information

| 6 status configuration registers: (for each channel)       | SCR0, SCR5 accessed by SOP command   |

|------------------------------------------------------------|--------------------------------------|

| 2 test registers:<br>(for each channel)                    | STCR0, STCR1 accessed by SOP command |

| 9 extended configuration registers:                        | XR0 XR8 accessed by XOP command      |

| 18 extended test registers:                                | XTR0 XTR17 accessed by XOP command   |

| 2 Transfer configuration registers: (for each channel)     | TCR0, TCR1 accessed by TOP command   |

| AC- and DC-Coefficient RAMs:                               | CRAMs accessed by COP command        |

| 2 coefficient set assignment registers: (for each channel) | CAR0, CAR1 accessed by COPI command  |

Overview of commands and registers via the IOM-2/ $\mu$ C Interface:

### **SOP Command**

| Bit              | 7 | 6  | 5 | 4 | 3   | 2     | 1     | 0     |

|------------------|---|----|---|---|-----|-------|-------|-------|

| SOP for SCR/STCR | В | RW | 0 | 1 | ATR | LSEL2 | LSEL1 | LSEL0 |

# **SOP Configuration Registers**

| Bit  | 7     | 6     | 5      | 4          | 3         | 2        | 1     | 0     |

|------|-------|-------|--------|------------|-----------|----------|-------|-------|

| SCR0 | POLNR | N/BB  | LB     | ETG2       | ETG1      | ENO      | ENTE  | COR   |

|      |       |       |        |            |           |          |       |       |

| SCR1 | TTXNO | TTX12 | NOSL   | SOREV      | ACT3      | ACT2     | QIO2D | QIO1D |

|      |       |       |        |            |           |          |       |       |

| SCR2 | VB/2M | ICONM | TEMPM  | FAILM      | MVAM      | LSUPM    | 1     | 1     |

|      |       |       |        |            |           |          |       |       |

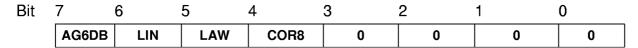

| SCR3 | AG6DB | LIN   | LAW    | COR8       | 0         | 0        | 0     | 0     |

|      |       |       |        |            |           |          |       |       |

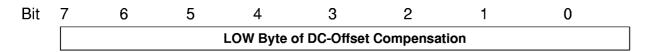

| SCR4 |       |       | LOW By | te of DC-O | fset Comp | ensation |       |       |

|      |       |       |        |            |           |          |       |       |

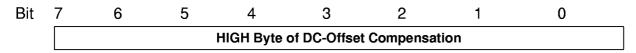

| SCR5 HIGH Byte of DC-Offset Compensation |

|------------------------------------------|

|------------------------------------------|

| STCR0 | FUSE3 | FUSE2 | FUSE1 | FUSE0 | 0    | 0    | 0     | 0     |

|-------|-------|-------|-------|-------|------|------|-------|-------|

|       |       |       |       |       |      |      |       |       |

| STCR1 | RSV5  | RSV4  | RSV3  | RSV2  | RSV1 | RSV0 | RSVU1 | RSVU0 |

### **XOP Command**

| Bit            | 7 | 6  | 5 | 4 | 3   | 2     | 1     | 0     |

|----------------|---|----|---|---|-----|-------|-------|-------|

| XOP for XR/XTR | 0 | RW | 1 | 0 | ATR | LSEL2 | LSEL1 | LSEL0 |

# **XOP Configuration Registers**

| Bit | 7                         | 6     | 5     | 4           | 3          | 2       | 1    | 0    |  |  |

|-----|---------------------------|-------|-------|-------------|------------|---------|------|------|--|--|

| XR0 | MIO4D                     | MIO3D | MIO2D | MIO1D       | MIO4       | MIO3    | MIO2 | MIO1 |  |  |

|     |                           |       |       |             |            |         |      |      |  |  |

| XR1 |                           | DUP   | GNK   |             |            | DI      | JP   |      |  |  |

|     |                           |       |       |             |            |         |      |      |  |  |

| XR2 | REXTEN                    | 0     | 0     | FIXC        | IDR        | EX-MCLK | 0    | 0    |  |  |

|     |                           |       |       |             |            |         |      |      |  |  |

| XR3 |                           |       | LOW   | Byte of AC- | CRAM che   | cksum   |      |      |  |  |

|     |                           |       |       |             |            |         |      |      |  |  |

| XR4 |                           |       | HIGH  | Byte of AC- | CRAM che   | ecksum  |      |      |  |  |

|     |                           |       |       |             |            |         |      |      |  |  |

| XR5 |                           |       | LOW   | Byte of AC- | CRAM che   | cksum   |      |      |  |  |

|     |                           |       |       |             |            |         |      |      |  |  |

| XR6 |                           |       | HIGH  | Byte of AC- | CRAM che   | ecksum  |      |      |  |  |

|     |                           |       |       |             |            |         |      |      |  |  |

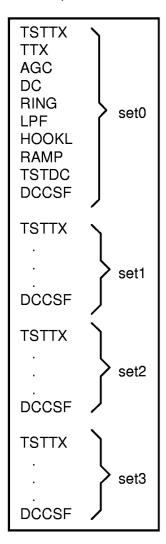

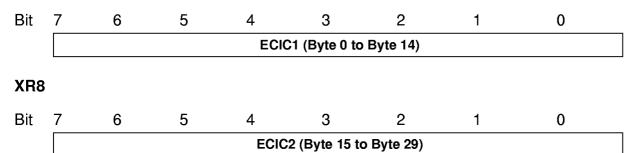

| XR7 | ECIC1 (Byte 0 to Byte 14) |       |       |             |            |         |      |      |  |  |

|     |                           |       |       |             |            |         |      |      |  |  |

| XR8 |                           |       | E     | CIC2 (Byte  | 15 to Byte | 29)     |      |      |  |  |

# **SIEMENS**

# **Programming the MuSLIC**

# **XOP Test Register**

| Bit    | 7         | 6         | 5         | 4                 | 3         | 2         | 1         | 0         |

|--------|-----------|-----------|-----------|-------------------|-----------|-----------|-----------|-----------|

| XTR0   | HIT       | HIR       | ELM       | SOFTON            | OPIM8M    | DLP03     | DLP5      | DISPOFI   |

|        |           |           |           |                   |           |           |           |           |

| XTR1   | CAL       | LMSEL1    | LMSEL0    | LMNOTCH           | LMBP      | LM2PCM    | PCM2DC    | ITIME     |

|        |           |           |           |                   |           |           |           |           |

| XTR2   | RING-ON   | DDCC      | DCAD16    | ERAMP             | ERECT     | AC-ADCPD  | AC-DACPD  | AFE-OFF   |

|        |           |           |           |                   |           |           |           |           |

| XTR3   | DHP-X     | DHP-R     | TH        | FRX               | FRR       | AX        | AR        | IM        |

|        |           |           |           | T                 | <u> </u>  |           |           |           |

| XTR4   | DLB-8M    | DLB-64K   | DLB-32K   | DLB-PCM           | ALB-8M    | ALB-64K   | ALB-8K    | DCHOLD    |

|        |           |           |           | T                 | T         |           |           |           |

| XTR5   | DC-DLB    | DC-ALB    | DC-ALBIT  | DC-ALBIL          | DC-ALBV   | DCLMU2    | DCLMU1    | DCLMU0    |

|        |           | <u> </u>  |           | Ι                 |           | <u> </u>  |           |           |

| XTR6   | TTXL      | DTTXL     | NOAGC     | ILITMUX           | COT16     | DITOFF    | AXG0      | ARG0      |

|        |           |           |           |                   | _         |           |           |           |

| XTR7   | QDETQ4    | QDETQ3    | QDETQ2    | QDETQ1            | 0         | 0         | 0         | 0         |

| \/TD-  |           |           |           | <b>TO 10</b> FID. |           |           |           |           |

| XTR8   | TQAP-FIR3 | TQAP-FIR2 | TQAP-FIR1 | TQAP-FIR0         | 0         | 0         | 0         | 0         |

| VTDO   |           | Fuse      | O A D 1   |                   |           |           | OA DO     |           |

| XTR9   |           | ruse      | QAPI      |                   |           | ruse      | QAP2      |           |

| XTR10  |           | Fuse (    | 7V D 3    |                   |           | Fuco      | QAP4      |           |

| XIIIIO |           | 1 036 (   | <u> </u>  |                   |           | 1 036     | QAI 4     |           |

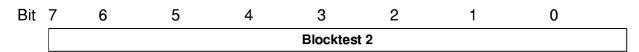

| XTR11  |           |           |           | Blockt            | test 1    |           |           |           |

| XIIII  |           |           |           | Bioon             |           |           |           |           |

| XTR12  |           |           |           | Blockt            | test 2    |           |           |           |

| XIIII2 |           |           |           | Bioon             |           |           |           |           |

| XTR13  |           |           |           | Blockt            | test 3    |           |           |           |

| ,,,,,, |           |           |           |                   |           |           |           |           |

| XTR14  | RSV1Q3    | RSV1Q2    | RSV1Q1    | RSV1Q0            | RSV2Q3    | RSV2Q2    | RSV2Q1    | RSV2Q0    |

|        |           |           |           |                   |           |           |           |           |

| XTR15  | RSV3Q3    | RSV3Q2    | RSV3Q1    | RSV3Q0            | RSV4Q3    | RSV4Q2    | RSV4Q1    | RSV4Q0    |

|        |           | l         |           | I                 | I         | l         |           |           |

| XTR16  | RSV5Q3    | RSV5Q2    | RSV5Q1    | RSV5Q0            | RSV6Q3    | RSV6Q2    | RSV6Q1    | RSV6Q0    |

|        |           | <b>I</b>  |           | I                 | I         | <b>I</b>  |           |           |

| XTR17  | DSVI I1O3 | RSVU1Q2   | DSVI I1O1 | DEVILION          | DCVILIOOO | DCV/LIOOO | DCV/110O4 | D07/11000 |

| /      | Inganias  | IUSANIAS  | novulai   | וטעוטעטח          | RSVUUQS   | RSYUUQZ   | RSYUUQII  | RSYUUQUI  |

#### **TOP Command**

Bit 7 6 5 4 3 2 1 0 0 R 1 1 0 0 LSEL1 LSEL0

#### **TOP Configuration Registers**

Bit 2 4 3 0 LSUP TCR0 VB/2 ICON **TEMP FAIL MVA RES** 0 NMVB/2 NMICON | NMTEMP **NMFAIL** TCR1 NMMVA NMLSUP RLM1 RLM0

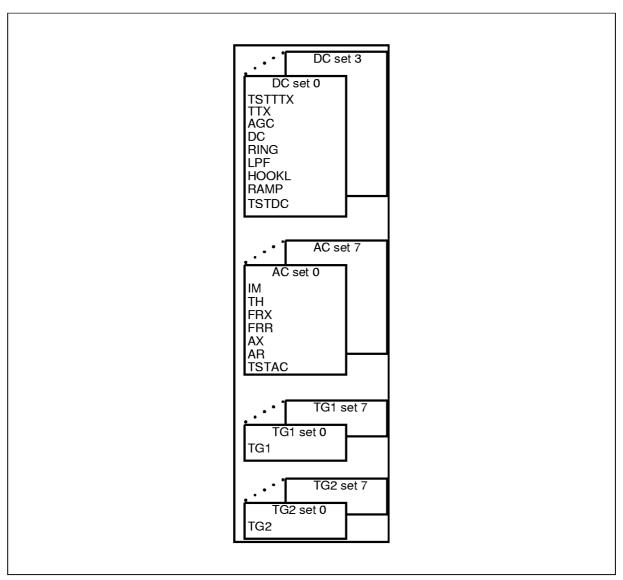

#### **COP Command**

Bit 7 5 3 2 **ICRAM** RW 0 0 0 1 WCRAM1 WCRAM0 SET2 SET1 SET0 CODE4 CODE3 CODE2 CODE1 CODE0

#### **COPI Command**

7

Bit

Bit 7 6 5 4 3 2 1 0 B RW 0 0 1 0 LSEL1 LSEL0

# **CAR Coefficient set Assignment Registers**

6

5

CAR0 HLOAD DC1 DC0 AC2 AC1 AC0 0 0 CAR1 TG1.2 TG1.1 TG1.0 TG2.2 TG2.1 TG2.0 0 0

3

2

1

0

4

#### 4.1.1 SOP Command

To modify or evaluate the MuSLIC status, individually for each channel, the contents of up to 6 configuration registers SCR0, ... SCR5 may be transferred to or from the MuSLIC. This is done by a SOP Command (status operation command).

With ATR = 1 and LSEL0 = 0/1 and LSEL1 = LSEL2 = 0 the registers STCR0, STCR1 can be set/read.

| Bit | 7 | 6  | 5 | 4 | 3   | 2     | 1     | 0     |

|-----|---|----|---|---|-----|-------|-------|-------|

|     | В | RW | 0 | 1 | ATR | LSEL2 | LSEL1 | LSEL0 |

**B** Broadcast

B = 0 Only one channel (time slot) is programmed

B = 1 All channels (up to 16) are programmed with the same

information

Read/Write Information: Enables reading from the MuSLIC or writing

information to the MuSLIC

RW = 0 Write to the MuSLIC

RW = 1 Read from the MuSLIC

ATR Access Test Register

ATR = 0 SCR0 ... SCR5 Registers are available

ATR = 1 STCR0, STCR1 Registers are read/writeable

**LSEL** Length select information

This field identifies the number of SOP Register

| ATR | LSEL 2 | LSEL 1 | LSEL 0 |              |

|-----|--------|--------|--------|--------------|

| 0   | 0      | 0      | 0      | SCR0         |

| 0   | 0      | 0      | 1      | SCR1         |

| 0   | 0      | 1      | 0      | SCR2         |

| 0   | 0      | 1      | 1      | SCR3         |

| 0   | 1      | 0      | 0      | SCR4         |

| 0   | 1      | 0      | 1      | SCR5         |

| 0   | 1      | 1      | 1      | SCR0 to SCR5 |

|     |        |        |        |              |

| 1   | 0      | 0      | 0      | STCR0        |

| 1   | 0      | 0      | 1      | STCR1        |

#### **SCR0 Configuration Register 0**

Configuration register SCR0 defines the basic feeding modes of the MuSLIC and enables/disables test features:

| Bit | 7     | 6    | 5  | 4    | 3    | 2   | 1    | 0   |

|-----|-------|------|----|------|------|-----|------|-----|

|     | POLNR | N/BB | LB | ETG2 | ETG1 | ENO | ENTE | COR |

Reset value: 00<sub>H</sub>

**POLNR** Normal or Reverse Polarity (see **chapter 5.4**)

POLNR = 0 sets the MuSLIC to Normal Polarity feeding POLNR = 1 sets the MuSLIC to Reverse Polarity feeding

N/BB MuSLIC is in normal or Boosted Battery mode (see chapter 5.4).

N/BB = 0 Normal feeding

N/BB = 1 Changes ternary interface to AHV-SLIC which sets the

AHV-SLIC to Boosted Battery mode

LB Handling of Loop Back functions for testing PCM loops

LB = 0 normal function

LB = 1 the desired Loop Back function is enabled

**ETG2** Enables programmable Test Tone Generator 2

ETG2 = 0 Test Tone Generator 2 is disabled ETG2 = 1 Test Tone Generator 2 is enabled

**ETG1** Enables programmable Test Tone Generator 1

ETG1 = 0 Test Tone Generator 1 is disabled ETG1 = 1 Test Tone Generator 1 is enabled

**ENO** Enables Offset compensation

ENO = 0 no DC offset compensation ENO = 1 DC offset compensation

**ENTE** Enables Test

ENTE = 0 normal operation

ENTE = 1 enables the test selected by the test registers (see

chapter 8)

COR Cut Off Receive Path for test reasons (see **chapter 8**)

COR = 0 Receive Path transmission is available

COR = 1 Receive Path is disabled

#### **SCR1 Configuration Register 1**

Configuration register SCR1 defines the meterpulse settings and the soft/hard reversal, linear mode and IO settings.

| Bit | 7     | 6     | 5    | 4     | 3    | 2    | 1     | 0     |

|-----|-------|-------|------|-------|------|------|-------|-------|

|     | TTXNO | TTX12 | NOSL | SOREV | АСТ3 | ACT2 | QIO2D | QIO1D |

Reset value: 00<sub>H</sub>

**TTXNO** Meterpulses are represented by teletax (TTX) with 12 or 16 kHz or with Reverse Polarity

TTXNO = 0 Meterpulses are represented with 12 kHz or 16 kHz

TTXNO = 1 Meterpulses are represented with Reverse Polarity

TTX12 Teletax-signal with 12 kHz or 16 kHz

TTX12 = 0 16 kHz teletax-signal TTX12 = 1 12 kHz teletax-signal

NOSL No slope: means that the ramping of teletax (TTX) signal is switched off

NOSL = 0 Slope of TTX-Signal is smoothNOSL = 1 Hard switch of TTX-Signal

**SOREV** Soft Reversal Meterpulses

SOREV = 0 hard reversal SOREV = 1 soft reversal

**ACT3** Active Mode with power save status of HV-SLIC (for future use)

ACT3 = 0 normal mode

ACT3 = 1 C1, C2 indicates the power save mode for the HV-SLIC

ACT2 Active Mode with power save status of HV-SLIC (for future use)

ACT2 = 0 normal mode

ACT2 = 1 C1, C2 indicates the power save mode for the HV-SLIC

QIO1D Direction for programmable IO - Pin of the QAP IO1

QIO1D = 0 sets the pin IO1 as an input QIO1D = 1 sets the pin IO1 as an output

QIO2D Direction for programmable IO - Pin of the QAP IO2

QIO2D = 0 sets the pin IO2 as an input QIO2D = 1 sets the pin IO2 as an output

04.97

### **SCR2 Configuration Register 2**

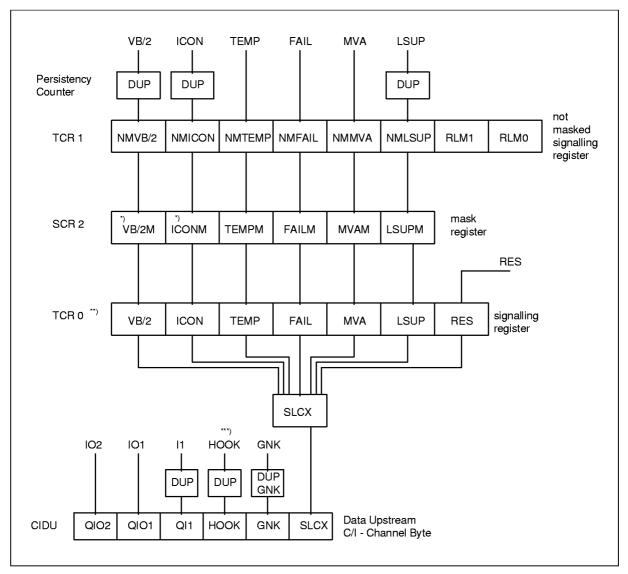

Configuration register SCR2 is the Mask register. Each bit of TCR0 (Signalling register) can be masked (except the RES bit); that means changes of such a 'masked bit' are not causing a change of the SLCX - bit (Data Upstream C/I-channel byte).

| Bit | 7     | 6     | 5     | 4     | 3    | 2     | 1 | 0 |

|-----|-------|-------|-------|-------|------|-------|---|---|

|     | VB/2M | ICONM | TEMPM | FAILM | MVAM | LSUPM | 1 | 1 |

Reset value: FF<sub>H</sub>

**VB/2M** Mask bit for half battery information

VB/2M = 0 each change of the VB/2 bit leads to an interrupt (SLCX-bit)

VB/2M = 1 changes of VB/2 bit are neglected

**ICONM** Mask bit for constant current information

ICONM = 0 each change of the ICON bit leads to an interrupt (SLCX-bit)

ICONM = 1 changes of ICON bit are neglected

**TEMPM** Mask bit for over temperature information

TEMPM = 0 each change of the TEMP bit leads to an interrupt

(SLCX-bit)

TEMPM = 1 changes of TEMP bit are neglected

**FAILM** Mask bit for clock fail information

FAILM = 0 each change of the FAIL bit leads to an interrupt (SLCX-bit)

FAILM = 1 changes of FAIL bit are neglected

**MVAM** Mask bit for internal measurement results

MVAM = 0 each change of the MVA bit leads to an interrupt (SLCX-bit)

MVAM = 1 changes of the MVA bit are neglected

**LSUPM** Mask bit for line supervision

LSUPM = 0 each change of the LSUP bit leads to an interrupt

(SLCX-bit)

LSUPM = 1 changes of the LSUP bit are neglected

Information about changing half battery- and constant current- information will be neglected on both of the Power Down and the Ringing state.

### **SCR3 Configuration Register**

Reset value: 00<sub>H</sub>

**AG6DB** Fixed gain in the transmit path.

AG6DB = 0 0 dB gain AG6DB = 1 + 6 dB gain

**LIN** Linear mode selection (16 bit linear information in voice channel A (upper

byte) and B (lower byte)

LIN = 0 PCM-mode is selected LIN = 1 linear mode is selected

**LAW** PCM-law selection

LAW = 0 A-Law is selected

LAW = 1  $\mu$ -Law is selected ( $\mu$ 255 PCM)

COR8 Cut off receive (voice only)

COR8 = 0 normal operation

COR8 = 1 cut off receive is enabled

## **SCR4 and SCR5 Configuration Register**

These two registers content the DC offset bytes. They can be used one by one. Activation is controlled by the ENO bit (SCR0-2)

#### SCR4

Reset value: 00<sub>H</sub>

#### SCR<sub>5</sub>

Reset value: 00<sub>H</sub>

### STCR0 Test Configuration Register 0

The Test Configuration register STCR0 is used for fuse operation and test only.

| Bit | 7     | 6     | 5     | 4     | 3 | 2 | 1 | 0 |

|-----|-------|-------|-------|-------|---|---|---|---|

|     | FUSE3 | FUSE2 | FUSE1 | FUSE0 | 0 | 0 | 0 | 0 |

Reset value: 00<sub>H</sub>

FUSE0 to FUSE3 Information for fuse operation

### **STCR1 Test Configuration Register 1**

The Test Configuration register STCR1 is used for reserved operations of the PEB 3465 (QAP).

| Bit | 7    | 6    | 5    | 4    | 3    | 2    | 1     | 0     |

|-----|------|------|------|------|------|------|-------|-------|

|     | RSV5 | RSV4 | RSV3 | RSV2 | RSV1 | RSV0 | RSVU1 | RSVU2 |

Reset value: 00<sub>H</sub>

**RSV0 to RSV5** from PEB 31665 to PEB 3465

**RSVU0 to RSVU1** from PEB 3465 to PEB 31665

#### 4.1.2 XOP Command

To modify or evaluate test configurations, to select special functions, to control the coefficient RAMs, to get information for fusing and ECIC and other common functions up to 15 Bytes maybe transferred to or from the MuSLIC, using the XOP Command (extended operation command).

| Bit | 7 | 6  | 5 | 4 | 3   | 2     | 1     | 0     |

|-----|---|----|---|---|-----|-------|-------|-------|

|     | 0 | RW | 1 | 0 | ATR | LSEL2 | LSEL1 | LSEL0 |

**RW** Read/Write Information: Enables reading from the MuSLIC or writing information to the MuSLIC

RW = 0 Write to the MuSLIC

RW = 1 Read from the MuSLIC

**LSEL** Length select information.

This field identifies the subsequent data bytes.

| ATR | LSEL 2 | LSEL 1 | LSEL 0 |                                    |

|-----|--------|--------|--------|------------------------------------|

| 0   | 0      | 0      | 0      | XR0                                |

| 0   | 0      | 0      | 1      | XR1                                |

| 0   | 0      | 1      | 0      | XR2                                |

| 0   | 0      | 1      | 1      | AC-RAM + DC-RAM Checksum           |

| 0   | 1      | 0      | 0      | AC-RAM Checksum                    |

| 0   | 1      | 0      | 1      | DC-RAM Checksum                    |

| 0   | 1      | 1      | 0      | ECIC1 (0 to 14)                    |

| 0   | 1      | 1      | 1      | ECIC2 (15 to 29)                   |

| 1   | 0      | 0      | 0      | XTR0                               |

| 1   | 0      | 0      | 1      | XTR1 and XTR2                      |

| 1   | 0      | 1      | 0      | XTR0 to XTR8                       |

| 1   | 0      | 1      | 1      | Fuse register 0 to Fuse register 1 |

| 1   | 1      | 0      | 0      | Blocktest 1 to Blocktest 3         |

| 1   | 1      | 0      | 1      | XTR14 to XTR17                     |

| 1   | 1      | 1      | 0      | RESERVED                           |

| 1   | 1      | 1      | 1      | RESERVED                           |

#### **XR0 Extended Operation Register 0**

Extended Operation Register 0 defines the four IO-pins of the MuPP.

| Bit | 7     | 6     | 5     | 4     | 3    | 2    | 1    | 0    |

|-----|-------|-------|-------|-------|------|------|------|------|

|     | MIO4D | MIO3D | MIO2D | MIO1D | MIO4 | MIO3 | MIO2 | MIO1 |

Reset value: 00<sub>H</sub>

MIOID Direction for programmable IO - Pins of the MuPP IO1 to IO4

MIOiD = 0 sets the pin IOi as an input MIOiD = 1 sets the pin IOi as an output

MIOi Value of programmable IO - Pins of the MuPP IO1 to IO4

MIOi = 0 sets the pin IOi to LOW or if it is read it is LOW MIOi = 1 sets the pin IOi to HIGH or if it is read it is HIGH

If the bit REXTEN (XR2-7) is set to 1 (Unbalanced Ringing) the MIO1 pin is switched to the ring pulse control function. Thus a zero-crossing signal connected to the MIO1 (combined with the Ringing Mode, burst on/off) generates a correct switching signal for the ringer relay sent on QIO1 of the selected subscriber line (see **chapter 4.2** and **chapter 5.5**).

If the bit EX-MCLK (XR2-2) and TST1 pin (No.26) are set to 1 and the MIO2 pin is set as an input the MuPP is ready for external clocking (32 MHz) (the internal PLL is shut down).

If the TST1 pin (No.26) and the bit EX-MCLK (XR-2) is set to 1 and the MIO2 pin is set as an output the 32 MHz clock (output of the internal PLL) is on the MIO2 pin.

### **XR1 Extended Operation Register 1**

Extended Operation Register 1 defines the Data Upstream Persistency Counters.

| Bit | 7 | 6 | 5      | 4 | 3 | 2 | 1   | 0 |

|-----|---|---|--------|---|---|---|-----|---|

|     |   |   | DUPGNK |   |   |   | DUP |   |

Reset value: 5A<sub>H</sub>

#### DUPGNK

To restrict the rate of upstream C/I-bit changes, deglitching (persistence checking) of the status information from the MuSLIC may be applied. New status information will be transmitted upstream, after it has been stable for N milliseconds. N is binary programmable in the range of 4 to 60 ms in steps of 4 ms, with DUPGNK =  $0_H$  the deglitching is disabled.

Reset value is 20 ms.

The HOOK bit (for external indication) and the GNK bit are influenced.

(Detailed info see **chapter 4.2**, and **figure 23**.)

#### **DUP**

To restrict the rate of upstream C/I-bit changes, deglitching (persistence checking) of the status information from the MuSLIC may be applied. New status information will be transmitted upstream, after it has been stable for N milliseconds. N is binary programmable in the range of 1 to 15 ms in steps of 1 ms; with DUP = 0h the deglitching is disabled.

Reset value is 10 ms.

The HOOK, SLCX and the QI1-bits are influenced (different counters but same programming).

(Detailed info see chapter 4.2, and figure 23.)

#### **XR2 Extended Operation Register 2**

Extended Operation Register 2 defines basic operations for all channels.

| Bit | 7      | 6 | 5 | 4    | 3   | 2       | 1 | 0 |

|-----|--------|---|---|------|-----|---------|---|---|

|     | REXTEN | 0 | 0 | FIXC | IDR | EX-MCLK | 0 | 0 |

Reset value: 10<sub>H</sub>

**REXTEN** External Ringing Mode Enabled (see chapter 5.5)

REXTEN = 0 use internal ringing mode REXTEN = 1 use external ringing mode

**FIXC** The MuSLIC uses either fixed coefficients or the programmed ones.

FIXC = 0 programmed coefficients used

FIXC = 1 fixed coefficients used

IDR Initializes Data RAM

IDR = 0 normal operation is selected

IDR = 1 content of Data RAM is set to 0 (for test purposes)

**EX-MCLK** Possibility to provide the MuSLIC with an external clock (see XR0)

EX-MCLK = 0 normal operation is selected

EX-MCLK = 1 internal PLL is shut down or internal clock is connected to

the pin MIO2, respectively (see XR0)

### XR3 TO XR6 Extended Operation Registers 3 to 6

XR3 to XR6 are the checksums of all the Coefficient bytes written into the Coefficient RAM (CRAM) of the MuPP by the COP-Command. Reading these bytes starts the sum generation. There are two identical blocks of CRAMs (time slot 0 to 7 and 8 to 15). Each reading alternates the block access.

#### XR3

| Bit | 7 | 6 | 5 | 4        | 3            | 2           | 1 | 0 |

|-----|---|---|---|----------|--------------|-------------|---|---|

|     |   |   |   | LOW Byt  | te of AC-CR/ | AM-checksur | n |   |

| XR4 |   |   |   |          |              |             |   |   |

| Bit | 7 | 6 | 5 | 4        | 3            | 2           | 1 | 0 |

|     |   |   |   | HIGH Byt | e of AC-CRA  | AM-checksur | n |   |

| XR5 |   |   |   |          |              |             |   |   |

| Bit | 7 | 6 | 5 | 4        | 3            | 2           | 1 | 0 |

|     |   |   |   | LOW Byt  | te of DC-CR/ | AM-checksur | n |   |

| XR6 |   |   |   |          |              |             |   |   |

| Bit | 7 | 6 | 5 | 4        | 3            | 2           | 1 | 0 |

|     |   |   |   | HIGH Byt | te of DC-CR/ | AM-checksu  | m |   |

(Algorithm of defining the checksum:  $x^{16} + x^{10} + x^7 + x + 1$ )

(With that algorithm you can reach a fault coverage of: 1-2<sup>-15</sup>)

Sum generation is done in the following manner (see **chapter 4.1.4**)

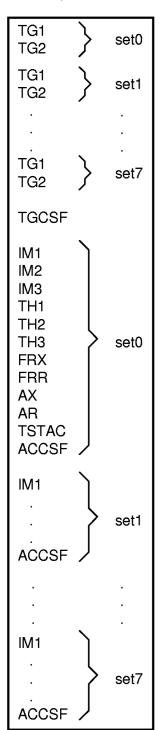

#### **AC-CRAM-Checksum**

The sequence of the coefficients is:

#### DC-RAM-Checksum

The sequence of the coefficients is:

Using the "checksum fill" Bytes (TGCSF, ACCSF, DCCSF) it is possible to create a fixed set-checksum independent of changed coefficients.

#### XR7 and XR8 Extended Operation Register 7 to 8

Each of these two registers feasibles to read 15 bytes of design/status information generated by an external ASIC. More details about the extended IOM-2 Channel Identification see **chapter 10**.

#### XR7

XR7 and XR8 shows the data stream of the input pin ID0. If the input pins ID1, ID2 and ID3 = 1, ID0 works as a serial input controlled by FSC and DCL (see **chapter 10**).

Reading XR7 or XR8 15 bytes each will be transferred from ID0 to IOM-2 Interface Monitor channel.

### XTR0 Extended Operation Test Register 0

Extended Operation Test Register XTR0 defines testing features.

| Bit | 7   | 6   | 5   | 4      | 3      | 2     | 1    | 0       |

|-----|-----|-----|-----|--------|--------|-------|------|---------|

|     | HIT | HIR | ELM | SOFTON | ОРІМ8М | DLP03 | DLP5 | DISPOFI |

Reset value: 00<sub>H</sub>

HIT for AHV-SLIC test functions

HIT = 0 normal operation

HIT = 1 changes HV-interface (C1,C2) which set the TIP wire to

high impedance

HIR for AHV-SLIC test functions

HIR = 0 normal operation

HIR= 1 changes HV-interface (C1,C2) which set the RING wire to

high impedance

# **SIEMENS**

### **Programming the MuSLIC**

**ELM** Enable level meter

ELM = 0 normal operation

if LM2PCM = 1 the input to the Levelmeter is switched to

PCM Voice-Channel

ELM = 1 level meter function is enabled

if LM2PCM = 1 the output of the Levelmeter is switched to

PCM Voice-Channel

**SOFTON** SW-fuses are activated in the PEB 3465

SOFTON = 0 HW-fuses are activated SOFTON = 1 SW-fuses are activated

**OPIM8M** Open fast digital Impedance Matching Loop (IM8M)

OPIM8M = 0 normal operation

OPIM8M = 1 opens fast digital IM-Loop ( $H_{IM8M} = 0$ )

**DLP03** Disable LP03-lowpass

DLP03 = 0 normal operation

DLP03 = 1 disables programmable lowpass ( $H_{LP03} = 1$ )

**DLP5** Disable LP5-lowpass

DLP5 = 0 normal operation

DLP5 = 1 disables programmable lowpass ( $H_{LP5} = 1$ )

**DISPOFI** Disable Postfilter (DC path)

DISPOFI = 0 normal operation DISPOFI = 1 disables postfilter

### XTR1 Extended Operation Test Register 1

XTR1 controls the level meter functions

Bit

7

6

5

4

3

2

1

0

CAL

LMSEL1

LMSEL0

LMNOTCH

LMBP

LM2PCM

PCM2DC

ITIME

Reset value: 00<sub>H</sub>

**CAL** Enable level meter result register

CAL = 0 normal operation (offset register - SCR4/SCR5 - is

read)

CAL = 1 levelmeter result register is read

**LMSEL** selects Levelmeter and Thresholdpairs

LMSEL1 LMSEL0

0 0 DC-Levelmeter Thresholdpair 0

0 1 DC-Levelmeter Thresholdpair 1

1 0 AC-Levelmeter

1 1 TTX-Levelmeter

**LMNOTCH** Bandpass or Notchfilter Function for Levelmetering AC

LMNOTCH = 0 Bandpass Function LMNOTCH = 1 Notchfilter Function

**LMBP** Activates the Bandpass or Notchfilter in the AC Transmit Path

LMBP = 0 normal operation

LMBP = 1 Bandpass/Notchfilter enabled

**LM2PCM** Switches the selected Levelmeter Signal to the PCM Voice-Channel

LM2PCM = 0 normal operation

LM2PCM = 1 switches the selected Levelmetersignal to the PCM

Voice-Channel

**PCM2DC** switches the Receive PCM Voice-Channel to DC-Output

PCM2DC = 0 normal operation

PCM2DC = 1 switches the Receive PCM Voice-Channel to

DC-Output

**ITIME** Integration time of AC and TTX Levelmeter

ITIME = 0 16 ms Integrationtime ITIME = 1 256 ms Integrationtime

# **SIEMENS**

### **Programming the MuSLIC**

#### XTR2 Extended Operation Test Register 2

Extended Operation Test Register XTR2 defines testing features (see chapter 8).

Bit

7

6

5

4

3

2

1

0

RING-ON

DDCC

DCAD16

ERAMP

ERECT

AC-ADCPD

AC-DACPD

AFE-OFF

Reset value: 00<sub>H</sub>

**RING-ON** Interrupt DC-characteristic and enables the Ringing Offset

RING-ON = 0 normal operation

RING-ON = 1 Interrupts DC-loop (HDCC = 0) and enables the

Ringing Offset

**DDCC** Disable DC-characteristic

DDCC = 0 normal operation

DDCC = 1 disables DC-loop (HDCC = 1)

DCAD16 DC gain of 16 in AD direction

DCAD16 = 0 normal operation

DCAD16 = 1 gain of 16

**ERAMP** Enable Ramping generator

ERAMP = 0 ramping generator off ERAMP = 1 ramping generator on

**ERECT** Enable rectifier in DC-levelmeter

ERECT = 0 normal operation (HRECT = 1)

ERECT = 1 enables rectifier

**AC-ADCPD** ADC is set to power down (transmit path is opened)

AC-ADCPD = 0 normal operation

AC-ADCPD = 1 transmit path is inactive

**AC-DACPD** DAC is set to power down (receive path is opened)

AC-DACPD = 0 normal operation

AC-DACPD = 1 receive path is inactive

**AFE-OFF** Analog front end is activated or deactivated

AFE-OFF = 0 normal operation

AFE-OFF = 1 the analog front end is deactivated

#### **XTR3 Extended Operation Test Register 3**

Extended Operation Test Register XTR3 defines the basic MuSLIC settings which enable / disable the programmable digital filters.

| Bit | 7     | 6     | 5  | 4   | 3   | 2  | 1  | 0  |

|-----|-------|-------|----|-----|-----|----|----|----|

|     | DHP-X | DHP-R | TH | FRX | FRR | AX | AR | IM |

Reset value: 00<sub>H</sub>