n la primera parte de este blog conocimos los empaques o encapsulados Through-Hole; si no lo has visto te invitamos a leerlo en este enlace. Continuamos este interesante viaje con la tecnología empleada para el montaje de superficie.

El montaje superficial, conocido en inglés como SMT (surface-mount technology), surge como parte del avance de miniaturización de tecnología.

A diferencia de los elementos que necesitar perforar la placa PCB, en los dispositivos de montaje superficial o SMD (del inglés surface-mount device) las conexiones se realizan mediante contactos planos, una matriz de esferas en la parte inferior del encapsulado, o terminaciones metálicas en los bordes del componente.

Clasificación

Dentro de los semiconductores que emplean la tecnología de montaje superficial encontramos algunos sin pines clasificados por su tamaño.

De acuedo a la wikipedia los de tamaños de algunos son:

Componentes pasivos rectangulares (principalmente resistencias y condensadores):

- 01005 (métrica 0402) : 0.016″ × 0.008″ (0,4 mm × 0,2 mm) Potencia típica para resistencias 1/32 W.

- 0201 (métrica 0603) : 0.024″ × 0.012″ (0,6 mm × 0,3 mm) Potencia típica para resistencia 1/20 W.

- 0402 (métrica 1005) : 0.04″ × 0.02″ (1,0 mm × 0,5 mm) Potencia típica para resistencia 1/16 W.

- 0603 (métrica 1608) : 0.063″ × 0.031″ (1,6 mm × 0,8 mm) Potencia típica para resistencia 1/10 W.

- 0805 (métrica 2012) : 0.08″ × 0.05″ (2,0 mm × 1,25 mm) Potencia típica para resistencia 1/8 W.

- 1206 (métrica 3216) : 0.126″ × 0.063″ (3,2 mm × 1,6 mm) Potencia típica para resistencia 1/4 W.

- 1806 (métrica 4516) : 0.177″ × 0.063″ (4,5 mm × 1,6 mm)Potencia típica para resistencia 1/4 W.

- 1812 (métrica 4532) : 0.18″ × 0.12″ (4,5 mm × 3,2 mm) Potencia típica para resistencia 1/2 W.

- 2010 (métrica 5025) : 0.2″ × 0.1″ (5,0 mm × 2,5 mm)Potencia típica para resistencia 1/2 W.

- 2512 (métrica 6332) : 0.25″ × 0.12″ (6,35 mm × 3,0 mm)Potencia típica para resistencia 1 W.

Condensadores de Tantalio:1

- EIA 3216-12 (S, AVX S):2 3,2 mm × 1,6 mm × 1,2 mm.

- EIA 3216-18 (A, AVX A): 3,2 mm × 1,6 mm × 1,8 mm.

- EIA 3528-12 (T, AVX T): 3,5 mm × 2,8 mm × 1,2 mm.

- EIA 3528-21 (B, AVX B): 3,5 mm × 2,8 mm × 2,1 mm.

- EIA 6032-15 (U, AVX W): 6,0 mm × 3,2 mm × 1,5 mm.

- EIA 6032-28 (C, AVX C): 6,0 mm × 3,2 mm × 2,8 mm.

- EIA 7260-38 (E, AVX V): 7,2 mm × 6,0 mm × 3,8 mm.

- EIA 7343-20 (V, AVX Y): 7,3 mm × 4,3 mm × 2,0 mm.

- EIA 7343-31 (D, AVX D): 7,3 mm × 4,3 mm × 3,1 mm.

- EIA 7343-43 (X, AVX E): 7,3 mm × 4,3 mm × 4,3 mm

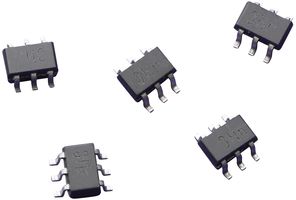

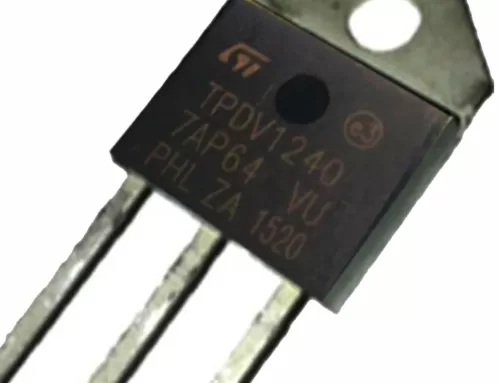

Encapsulados de tres terminales:

- SOT (Small-Outline Transistor): Para transistores.

- DPAK (TO-252): Discrete Packaging: Desarrollado por Motorola para soportar mayores potencias.

- D2PAK (TO-263): más grande que DPAK; es un análogo del encapsulado TO-220 de tecnología through-hole.

- D3PAK (TO-268): más grande que D2PAK.

Encapsulados con cuatro o más terminales:

Dual-in-line (DIL).

Con su forma rectangular, son similares a los DIP con pines en linea en dos de sus lados pero sus terminales tienen un doblez al final para facilitar su instalación con soldadura a la placa PCB.

- Small-Outline Integrated Circuit (SOIC). También llamados SOP.

- J-leaded Small Outline package (SOJ).

- TSOP (Thin Small-Outline Package), más delgado que SOIC y con menor espaciado entre pines.

- SSOP (Shrink Small-Outline Package): es una versión más pequeña del SOIC con 8 hasta 64 pines.

- TSSOP (Thin Shrink Small-Outline Package), similar al anterior con unespaciado de pine entre 0,5 o 0,65 mm.

- QSOP (Quarter-size Small-Outline Package).Tienen entre 16 a 28 pines.

- VSOP, más chico que QSOP.

Quad-in-line.

Con tendencia a ser cuadrados, generalmente tienen conexiones en sus cuatros lados.

- PLCC (Plastic Leaded Chip Carrier). también llamado Quad-Flat-J-Leg Chipcarrier (QFJ), es un encapsulado de circuito integrado, con un espaciado de pines de 0,05 pulgadas = 1,27 mm. El número de pines oscila entre 20 y 84. Los encapsulados PLCC pueden ser cuadrados o rectangulares. Su montaje pude ser tanto superficial o en zócalo para aquellos elementos que no resisten calor o requieran un fácil reemplazo.

- QFP (Quad Flat Package). Es la evolución de anterior habitualmente tiene de 44 a 200 pines, con una separación entre ellos de 0,4 a 1mm.

- LQFP (Low-profile Quad Flat Package). El espacio entre pines puede variar; los intervalos más comunes son 0,4; 0,5; 0,65 y 0,80 mm.

- PQFP (Plastic Quad Flat-Pack). Tiene entre 32 a 208 pines espaciados de 0,4 mm a 1mm.

- CQFP (Ceramic Quad Flat-Pack), como su nombre lo indica es cerámico, similar a PQFP.

- MQFP (Metric Quad Flat Pack). Viene en diferentes tamaños desde 10mm a los 40mm también hay variación en su grosor desde los 2 a los 3.5mm.

- TQFP (Thin Quad Flat Pack), versión más delgada de PQFP.

- QFN (Quad Flat-pack, No-leads), versión más pequeña y sin pines de QFP.

- LCC (Leadless Chip Carrier). Son una variante del PLCC

- PQFN (Power Quad Flat-pack, No-leads). Tienen un tamaño entre los 3×3 mm a 8×8 mm, libres de halógenos y plomo.

Te invitamos a visitar nuestra sección de Semiconductores donde encontrarás soluciones a tus necesidades electrónicas.

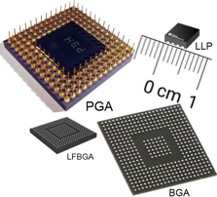

Matriciales o Grid arrays.

- PGA (Pin Grid Array). Son usados principalmente en microprocesadores de motherboards se caracterizan por tener una matriz de rejilla de pines.

- BGA (Ball Grid Array), Similar al anterior, posee “bolitas” en la parte inferior del encapsulado en lugar de pines.

- LFBGA (Low profile Fine pitch Ball Grid Array), igual a BGA pero más pequeño.

- CGA (Column Grid Array).

- CCGA (Ceramic Column Grid Array).

- μBGA (micro-BGA), el espaciado entre bolitas es menor a 1 mm.

- LLP (Lead Less Package).

En este manual encontrarás mayor información sobre los empaque de semiconductores usado por los fabricantes.